For decades, the worldwide electronics industry has produced a stream of products that continue to amaze us with their capabilities, their compactness, and their low price. This track record is due, in part, to an intricate set of interrelationships between a large number of hardware and software vendors who balance cooperative and competitive market strategies. Key elements in maintaining coordination among the many suppliers in this market are the industry standards governing all aspects of technology.

This article focuses on standards related to thermal characterization of integrated circuit devices, a very critical class of components. It pays particular attention to the activities of the JEDEC JC15.1 Subcommittee, which has played a leading role in generating and promoting thermal characterization standards.

Trends in Power and Thermal Standards

As the power levels in high performance integrated circuit devices have continued to march to the beat of Moore’s law, the demands placed on thermal standards have increased. [1]

In the 1980s, the dominant packaging technologies involved through-hole mounting of devices on motherboards with metallization on one side only. IC power levels were less than one Watt. The only thermal enhancement in plastic IC packages consisted of replacing the low-thermal-conductivity Alloy 42 used in leadframes with higher conductivity copper alloys.

At that time, the prevalent thermal standards were generated by SEMI. [2] The standards defined the natural convection, wind tunnel, and infinite cold plate test environments as well as thermal test die and test board design. These standards were appropriate for the technology of the time. However, they lacked sufficient breadth and precision to support the enhanced thermal requirements of the 1990s.

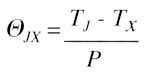

The thermal metrics were thermal resistances: JA and

JC.

JA is a measure of the ease of heat flow from the junction (active circuitry on the die surface) to air for a package mounted to a test board and located in either the natural convection chamber or a wind tunnel. Since the standard test environment and board design differ significantly from those in many applications, the proper use of

JA is to provide a thermal performance ranking of packages and not to simulate a particular end-use application.

JC indicates the ease of heat flow from the junction to the top or bottom surface of the package (the case), which, during the test, is kept in contact with an isothermal surface. This quantity relates to the thermal performance of a package when used with an external heat sink. [3]In a particular environment, the thermal resistance for heat to flow from the junction to location X is determined from the following equation:

|

where TJ is the junction temperature, TX is the temperature at the specified location, and P is the total dissipated power. The test environment is configured so that, to a good approximation, all of the heat flows to the indicated location.

These thermal metrics were used as stand-alone figures of merit. It was the job of the thermal engineer to relate the performance of a package in the standard test environment to that in a particular application.

The 1990s ushered in several developments in packaging technology: greater acceptance of copper-alloy leadframes and surface-mount technology, and the use of multi-layer boards incorporating copper planes for electrical power distribution. Surface-mount and multilayer board technologies were adopted for the purpose of increasing the device density on motherboards.However, they also provided an extra margin for the cooling of integrated circuits and established the motherboard as a key component from the viewpoint of electronics cooling.

Further increases in power up to 5 Watts were accommodated by enhancement of existing package designs by the insertion of metal heat spreaders.

In the late 1990s so-called laminate, or Ball Grid Array, packages began to penetrate the industry. These contain a miniature circuit board rather than a leadframe to route the electrical signals and use an array of solder balls to provide the electrical connection to the motherboard. This technology made possible a large increase in the number of leads per package while reducing the package footprint area. It also led to the development of many new package designs, customized for cost-effective operation in specific applications.

JEDEC Thermal Standards Committee

Since 1990, the JEDEC JC15.1 Subcommittee has been involved with the generation of thermal standards. Approximately 40 companies subscribe to this committee. They include semiconductor, packaging, and software companies. The charter of the committee is outlined as follows:

- It will generate thermal measurement and modeling standards for microelectronic packaging.

- These standards shall be meaningful, consistent, and proven to be scientifically sound.

- The standards will provide a common means of comparison of thermal phenomena for users of microelectronic packaging.

Consistent with this charter, the provisions of proposed standards are validated using round-robin testing and computer simulation.

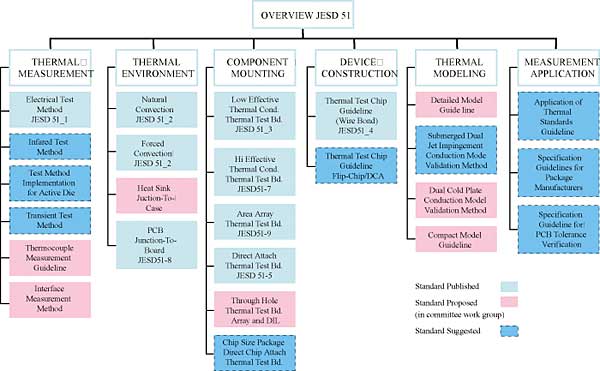

Figure 1 outlines the organization of the published, proposed, and suggested standards. [4]

Figure 1. Outline of published, proposed, and suggested standards — JEDEC JC15.1 Subcommittee.

Thermal Test Standards

The first four categories are applicable to test techniques: Thermal Measurement Method, Thermal Environment, Component Mounting, and Device Construction. The next category is Thermal Modeling and includes model validation. The last one is entitled Measurement Application and deals with relating test results to end-use environments, among others.

As is clear from the figure, all of the standards published to date deal with test issues. The intent was to begin in the spirit of previous standards, but to write them in a more precise fashion to reduce variability in test results from lab-to-lab. This was particularly evident in the test board standards, which were crafted to limit lab-to-lab variability to less than +/- 5%, a big improvement over the SEMI standards. [5]

The test standards are structured to provide a modular approach to testing. Together they cover all aspects of testing. The modular approach has the dual merits of providing adaptability to many situations and eliminating the need to rewrite the existing standards to accommodate a new measurement method, environment, mounting structure, or device construction.

The market realities of the 1990s required more accurate prediction of the junction temperature than was possible using a measured value of JA, tempered by engineering judgement. In response to this situation, three new thermal metrics were defined:

JB,

JB and

JT.

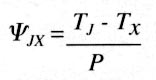

JB is a thermal resistance between the junction and the board. It is measured in an environment designed to extract nearly all the heat from the board, beyond the package periphery. The board temperature is measured on a trace located at the package centerline, 1 mm from the package body. For a peripheral leaded package with gull wing leads, the measurement location is the lead foot itself.The other two metrics,

JB and

JT, are referred to as thermal characterization parameters. The formula for calculating an arbitrary

JX is as follows, where the symbols on the right side of the equation have the same meaning as in Eqn. 1.

|

The only difference between them is that in the measurement environment for a JX metric, only a fraction of the heat flows from the junction to location X. The locations of temperature measurement for

JB are the same as for

JB. However,

JB is measured in a natural convection or wind tunnel environment.Most, but not all, of the heat dissipated in the die flows to the board. The remainder flows out of the top of the package.

JT provides the correlation between the junction temperature and the temperature of the top center of the package in this same environment.The first two metrics

JB and

JB can serve a predictive function for the junction temperature in an application. [6] It is obvious that most application environments differ significantly from the standard test environment: different board size, many more heat sources, irregular air flows, etc. It turns out that all of these differences have a significant effect in the correlation between the junction temperature and the air temperature in the chassis.On the other hand, as long as the application board contains two internal planes with a thickness equal to that of the JEDEC board (35 �m, or 1 oz copper), the correlation between TJ and TB in the application environment correlates reasonably well with that determined in the standard test environment.

JT is used to determine the junction temperature in an end-use environment from a measurement of the temperature of the top of the package.

Thermal Model Standards and Guidelines

In recent months, the fifth category in Figure 1, that of Thermal Modeling, has begun to represent an increasing share on the committee’s agenda. This parallels the industry trend to depend more and more upon modeling to provide thermal characterizations of components due to the imperative for reducing the cycle time for product development.

The thinking of the committee is that thermal modeling techniques will continue to evolve at a rapid rate. Hence, any JEDEC document that attempted to standardize modeling procedures would be doomed to failure. A more productive course would be to issue guidelines that will apply to documentation of the procedure that is used and to the validation of the model. The hope is that a report adhering to these guidelines would provide readers with enough information so that they could understand in detail the assumptions and mechanics of the model and would be able to estimate the accuracy of the analysis.

One draft guideline applies to what are called detailed thermal models. These involve a mathematical representation of the package and, usually, a printed circuit board, in varying amounts of detail. The solution techniques involve finite element, finite difference, and thermal resistor network approaches. These models can contain upwards of 100,000 nodes and elements.

Another area of activity involves what are called Compact Thermal Models (CTMs). The initial development of these models was done under the auspices of the European DELPHI Consortium and continued under the SEED project [7-10] and in the ongoing PROFIT project, begun in January, 2000. [11] Their development was a response to the need to perform more rapid and accurate analyses at the system level.The CTMs are intended to serve as a data set, which is generated by the component supplier and which can be readily inserted into a system-level simulation. Hence, the Compact Thermal Model approach not only represents a departure from traditional analysis methods but also a clean division of labor between the component suppliers and the system manufacturer.

These models differ in many ways from the more traditional detailed models. In conventional terms a CTM can be described as a thermal resistor network with a relatively small number of nodes (up to approximately 5 – 10), which accurately represents the package under many boundary conditions. The network elements are more precisely called links since they represent a temperature correlation between two regions of the package and do not always correspond to a physical heat flow path. [8] The precise format of these models is still under development. [12]

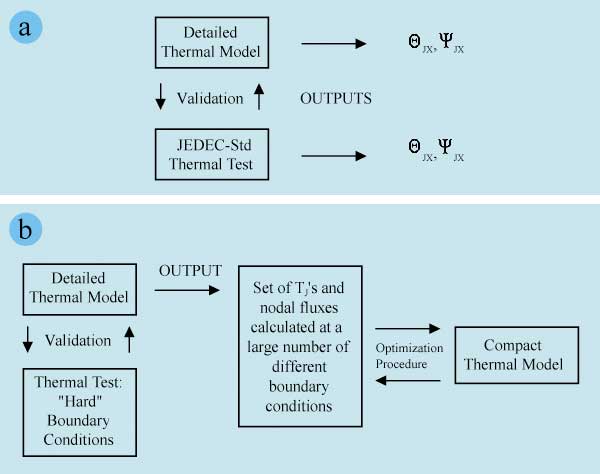

The CTM approach represents a radical departure from traditional methods of package characterization. The two approaches are outlined symbolically in Figure 2.

Figure 2. Flow charts for model validation and generation: a) Traditional approach. b) DELPHI Compact Model approach.Figure 2a outlines what is called here the traditional approach. The detailed model is validated by a comparison of its predictions with the results of JEDEC-standard tests. The possible test configurations are convective environments as well as environments that provide conduction, or “hard,” boundary conditions.Once the model is validated, it can be used to simulate any of the standard tests. Hence, the output of both the test and the model are the standard thermal metrics, QJA, QJB, QJC, CJB, etc. These all have an easily understood physical basis and can be used in simple engineering calculations. A drawback of these metrics is that they do not lend themselves to representation of the package in an arbitrary system-level simulation.

Figure 2b illustrates the procedure in implementing the DELPHI Compact Model approach. Here, the testing is used only as a means of validating the results of the detailed model. The test configurations are limited to “hard” boundary conditions.The typical test environment is called the Double Cold Plate (DCP). [10, 11] The DCP fixturing can be configured to alternately extract the heat from the package by way of its top and bottom surfaces, top surface only, bottom surface only, and the leads.The intent is to exercise the model with different heat flow configurations that would span the practical possibilities. Once validated, the detailed model is run in a batch mode to output calculated values of junction temperature and surface node fluxes under a large number of combinations of boundary conditions (typically in the range of 40 – 99). [8] Research is ongoing to confirm that this number can be substantially reduced. These configurations are represented as different heat transfer coefficients applied to the various surface regions of the package. The same boundary conditions are applied to the compact model. Using an optimization procedure, values of the links are selected which minimize the discrepancy between the predictions of the detailed model and the compact model. Compact models resulting from this procedure have been shown to be very nearly boundary-condition independent. Another promising approach emanating from the PROFIT project is to extract models from a series of time-dependent measurements. [13]

The compact model can then, in principal, be imported into the system-level simulation software. At that point, actual values of junction temperature can be generated.The compact model approach places a much greater emphasis on simulation than does the traditional approach.Both the process and the results are much more abstract than with the traditional approach. A 10-link thermal compact model does not lend itself to a “back of the envelope” calculation as readily as a QJB value, for example.

JC15.1 Compact Model Agenda

The electronic marketplace of today places serious demands on thermal engineers.These demands include reduced product development cycle time, increased power levels, greater cost pressures, tighter performance design windows (over-design costs money; under-design disappoints customers), and the proliferation of package designs. These conditions make traditional methods of package-level and system-level thermal analysis impractical and demand increased levels of automation in all phases of thermal characterization. It is clear that to achieve adequate levels of efficiency in this process, component suppliers will be compelled to provide thermal representations of their products, which can be readily imported into system-level simulation tools.

In response to these imperatives, the JC15.1 is pursuing a broad agenda intended to enlighten its members regarding the current state of the art in thermal compact models. Individuals from European companies that participated in the DELPHI and SEED projects have played an important role in this process.

Furthermore, with the involvement of representatives of 10 member companies, the committee is conducting parallel JEDEC-standard and DCP tests on selected package formats with concurrent detailed modeling. These results will provide the basis of a subsequent compact model evaluation.

Working together, the US and European participants on the committee are exploring methods of achieving greater efficiencies in these methodologies such as the use of printed circuit board technologies for the fabrication of package fixturing in the DCP tests. The committee is also exploring procedures to provide a migration path to bridge the gap between the traditional and CTM approaches until the CTM approach can be fully established. These include the use of JEDEC-standard tests in detailed model validation and the use of 2-resistor compact models generated directly from JEDEC-standard tests.

The hope is that this effort will promote the generation of appropriate and robust standards and guidelines to assist the propagation of compact model methodologies throughout the electronics industry.

Future Needs

In order for thermal engineers to respond effectively to the demands of greater precision in less time, it will be necessary for the structural barriers that limit the efficiency of modeling to be considerably reduced.The required remedies will include:

- Robust interfaces between CAD software and thermal analysis software tools at both the package and system levels.

- More efficient meshing algorithms optimized for the thin-layered structures of modern electronic components.

- The establishment of compact models as the dominant method of quantifying the thermal performance of electronic components.

- Web-based distribution of compact models.

- Robust algorithms for incorporating compact models into system level simulation software.

Fortunately for thermal engineers, Moore’s Law provides not only a head wind but also a tail wind in the relentless race toward greater performance. Confronted with the challenge of continually increasing power levels, thermal engineers have at their disposal ever more powerful and cheaper computers. The hardware will be there to support the evolution in software described above. The real challenge will be for the software companies to build the required links between the now isolated islands of computational capability.

References

1. K. Azar, “The History of Power Dissipation,” Electronics Cooling Magazine, Vol. 7, No. 1, (January, 2000), pp 42-50.

2.Semiconductor Equipment and Materials International (www.semi.org).

3.Examples in the use of standard thermal metrics (QJA, QJC, CJB, and CJT) can be found in “Calculation Corner”, a regular column by the author in this magazine, in the May and September issues, 1999, and the May issue, 2000.

4. All published JEDEC thermal standards are available for download at no charge at the organization’s web site (www.jedec.org).

5. D. Edwards, “Development of JEDEC Standard Thermal Measurement Test Boards,” Proceedings, SEMI-THERM XII Conference, March, 1996, pp. 183-190.

6. B. Joiner, “Use of Junction-to-Board Thermal Resistance in Predictive Engineering,” Electronics Cooling Magazine, Vol. 5, No. 1 (January, 1999), pp. 14-17.

7. H. Rosten, C. Lasance, and J. Parry, “The World of Thermal Characterization According to DELPHI – Part I: Background to DELPHI,” IEEE Trans. CHMT, Vol. 20, 1997, pp. 384-391.

8. C. Lasance, D. den Hertog, and P. Stehouwer, “Creation and Evaluation of Compact Models for Thermal Characterization Using Dedicated Optimisation Software,” Proceedings, SEMI-THERM XV Conference, March, 1999, pp. 189-200.

9. H. Pape and G. Noebauer, “Thermal Characterization of Active Components,” Electronics Cooling Magazine, Vol. 4, No. 2 (May, 1999), pp. 38-43.

10. H. Pape and G. Noebauer, “Generation and Verification of Boundary Independent Compact Thermal Models for Active Components According to the DELPHI/SEED Methods,” ,” Proceedings, SEMI-THERM XV Conference, March, 1999, pp.201-211.

11. www.extra.research.philips.com/euprojects/profit/

12. A. Aranyosi, A. Ortega, J. Evans, T. Tarter, J. Pursel, and J. Radhakrishnan, “Development of Compact Thermal Models for Advanced Electronic Packaging: Methodology and Experimental Validation for a Single-Chip CPGA Package,” Proceedings, Itherm 2000 Conference, May, 2000, pp. 225-232.

13. M. Rencz, V. Szekely, E. Kollar, “Measuring Dynamic Thermal Multiport Parameters of IC Packages”, Proceedings, 6th THERMINIC Workshop, Budapest, 2000, pp.244-249.