As more and more integrated circuits dissipate power at levels once reserved for power discrete devices, junction-to-case thermal resistance (JC or R

JC) remains as important as ever. The difficulties in making

JC measurements often leads to values that do not accurately indicate true junction temperature (TJ). The measurement difficulties are usually two-fold. First is establishing an environmental condition in which the heat generated within the package can only leave the package through the package surface used for heat sinking purposes. This problem is particularly acute for cases in which significant heat conduction occurs through the package leads or contacts; BGA packages for example. However, the issue of parasitic heat loss through other paths from the device junction is beyond the scope of this article. The second measurement difficulty, and the main focus of this article, lies in being able to measure the package (or case) temperature while still meeting the environmental conditions.

The question of how to make JC measurements is still being debated in the EIA/JEDEC JC15.1 sub-committee on package thermal issues and no standard has resulted to date. The approach currently being considered by the subcommittee is based on attaching a thermocouple (or other temperature sensor) to the package surface and making a surface temperature measurement after establishment of a steady-state condition with power applied to the package. The difficulties of this approach are discussed below. The SEMI standard (G30-88) lacks sufficient detail to insure repeatable and reproducible results. The purpose of this article is to present a measurement approach concept that could lead to a standard test method.

Defining the Problem

JESD51-1 provides a definition of JC as follows:thermal resistance, junction-to-case: The thermal resistance from the operating portion of a semiconductor device to outside surface of the package (case) closest to the chip mounting area when that same surface is properly heat sunk so as to minimize temperature variation across that surface.

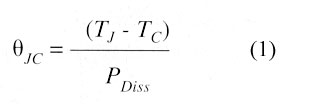

In equation form, thermal resistance from junction-to-case is:

|

where TJ = Junction Temperature

TC = Case Temperature

PDiss = Power Dissipation that produced the rise in TJ

Ignoring the problem that the package (case) surface closest to the chip mounting area may not actually be the surface suitable for heat sinking, there is still the problem of how to insure an isothermal heat sink mounting surface. Any attempt to measure the surface temperature and keep it isothermal at the same time runs into many difficulties. A proper cold plate mounted on the surface can keep the surface isothermal provided that there is good mating between the package and heat sink surfaces.

However, mounting a thermocouple (or some other temperature measuring tool) on the package surface requires either a hole through the heat sink or a groove in the heat sink to pass the thermocouple leads from the mounting area. In either case, the finite size of the hole or groove insures that the package surface will not be completely isothermal. There is also the non-trivial problem of insuring that the thermocouple is actually measuring the package surface temperature and not the temperature of the heat sink.

Add to this problem the meticulous labor of mounting the thermocouple and modifying the cold plate, which translates into a cost factor and the potential for result variation due to differences in labor skill levels.

Measurement Alternative

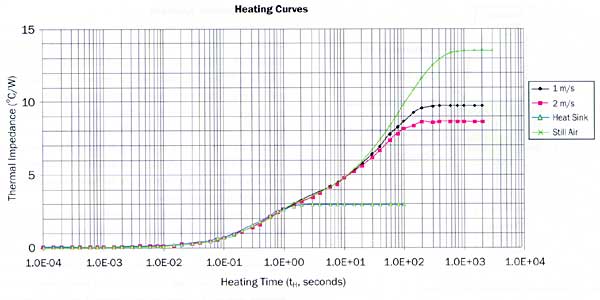

The above definition of JC provides a clue as to a useful alternative measurement approach. Whenever TJ is higher than the package surface temperature, heat will propagate from the junction (i.e., the source of the heat) through the various materials inside the package to the outer surface of the package. This propagation takes a finite amount of time and makes it possible to use time to determine how far the heat has traveled from the junction outward. As long as the heat has just propagated to the package surface, the package surface will essentially be isothermal and whatever boundary condition imposed on the surface will have no impact on the thermal performance of the package.If the heat generated inside the package continues past the propagation time to the package surface, then the applied boundary condition will determine the ultimate value of TJ. The best way to see this phenomena is by the use of Heating Curves, which show

TJ (or something proportional to

TJ, such as instantaneous thermal impedance (Zi

JX)) [y-axis] as a function of time that power has been applied to the chip within the package [x-axis]. The time axis is usually logarithmic because of the dynamic range and is refered to as Heating Time (tH).This heat propagation phenomenon is clearly demonstrated in Figure 1. Four separate curves are shown for a specific package/chip combination with the same test conditions and different environmental conditions – one for a cold plate (heat sink) measurement, one for a natural convection measurement, and two for forced convection measurements at different air velocities. Up until the Heating Time (tH) reaches approximately 1.5 seconds, all four curves coincide.

|

Figure 1. Heating Curves: Typical heating curves generated for a thermally-enhanced 480 BGA package mounted on a JEDEC high thermal conductivity thermal test board. Power dissipation for all curves is approximately 3.7 W.Beyond that value of tH, the curve for the cold plate environmental condition diverges and reaches a plateau corresponding to heat being transferred into the cold plate; the cold plate is maintained at a constant temperature and has sufficient thermal mass so that its temperature doesn’t change for tH values out to at least 100 seconds. The other three curves remain coincident for tH values up until the heat propagation is impacted by the next environmental condition – in this case, the impact of the forced convection is observed at about 20 seconds.

The key to using the heat propagation approach to determine JC is to know exactly when the heat has reached the package surface. A quick response to this problem would be to mount a thermocouple on the package surface, apply power to the chip/package combination, and note the time instant when the package temperature starts to change. This approach does not work for two reasons: first, the temperature measuring equipment usually has some finite time lag in its response; and second, the package surface probably won’t be isothermal. Any attempt to keep the package surface isothermal and measure the surface temperature results in the same kind of problems associated with the traditional methods for

JC measurements.

Thermal Transient Approach

A better approach to this measurement alternative is to use a thermal transient method. This method measures changes in TJ (using the temperature sensitive parameter method described in JESD51-1) as a function of the time that power is applied to the chip/package combination. The method requires instrumentation that can apply the heating and measurement conditions and make the appropriate measurements fast enough, with sufficient accuracy, over the time range of interest. While it is possible to simply apply power to the package under test and make continuous measurements, this approach is only suitable for packages that have independent heating source and temperature sensor.

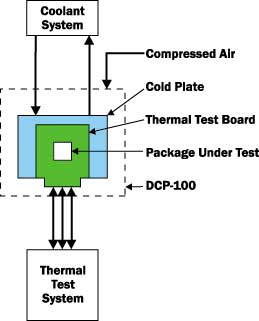

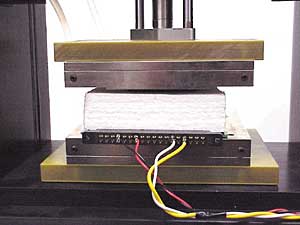

An alternative approach is to make repeat measurements of TJ for increasing periods of heating time, with sufficient time between each iteration to insure that TJ returns to its initial value at the beginning of the test process before the start of the next successive measurement. A cold plate (i.e., infinite heat sink) is mounted on the package surface. This insures an isothermal package surface and aids in determining when the heat has reached the package surface.Figure 2 shows a typical apparatus block diagram for making

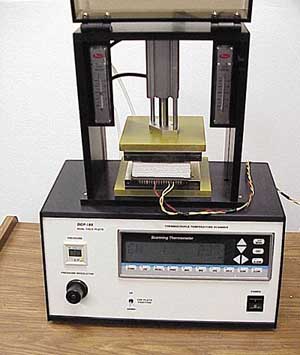

JC measurements using the thermal transient approach. The cold plate setup, shown in Figure 3, uses the bottom section of a dual cold plate test fixture (TEA’s DCP-100) for package mounting and the top section as a press to insure a known, fixed pressure on the package-to-cold plate interface. Figure 4 shows how a one inch thick piece of medium density Styrofoam isolates the top section from the back of the thermal test board to insure no heat removal from that path. The fixture contains instrumentation for monitoring the water flow into the cold plate and the cold plate surface temperature.

Figure 2. Measurement apparatus block diagram.

Figure 3. Test Setup: The DCP-100 dual cold plate test fixture set up for JC measurements using the bottom cold plate for heat sinking and the top cold plate as a pressure plate.

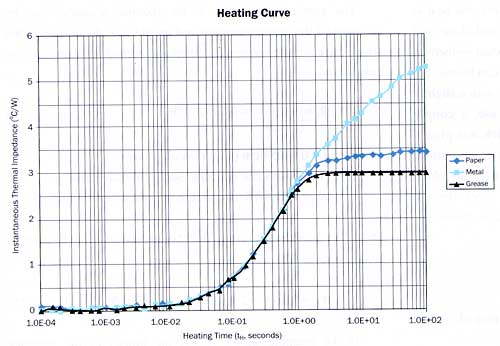

To demonstrate the sensitivity of the thermal transient method to package surface/cold plate interface variations, data was collected for three interface conditions. Figure 5 shows heating curves for a thermally-enchanted 480-ball, 1.27 mm ball pitch, 35 mm square BGA package mounted on a JESD51-9 high thermal conductivity thermal test board with 3.7 watts applied; interfaces are:

- 0.003″ (0.00762 cm) thick paper approximately 3.5″ (8.89 cm) square between package surface and cold plate

- Package top metal surface directly on cold plate surface

- Thin layer of thermal grease (Wakefield #120-2) between package surface and cold plate.

Figure 5. Thermal Impedance Curves: These heating curves show the impact of junction temperature rise for three different thermal interfaces between the package surface and the cold plate.The fixture’s air pressure was adjusted in each case to provide 100 psi (689.5 KP) of pressure on the interface, corresponding to approximately 44.3 pounds (0.197 KN) of force for the subject package. The heating curves for the three interface cases appear in Figure 5.

The heating curves for the conditions described show that heat has just started to reach the package surface in about one second when the curves start to deviate and, in the cold plate case, reaches an isothermal package surface condition, corresponding to the JC point, in approximately four seconds.

Data Correction

The actual data obtained from the thermal transient measurement can be broken into three parts:

JX =

JC +

i +

CP (2)where:

JX = the measured results

JC = the desired junction-to-case thermal resistance

i = the interface thermal resistance

CP = the Cold Plate thermal resistance

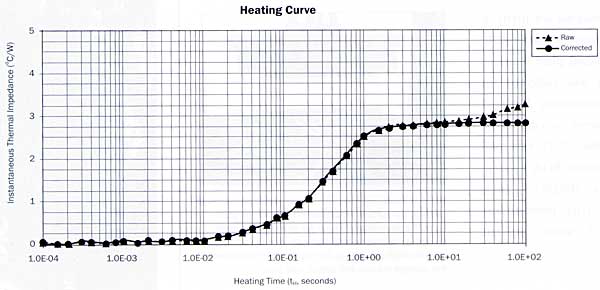

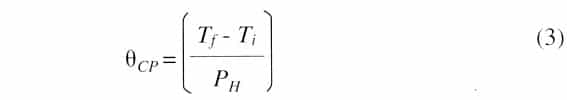

Figure 6. Heat Sink Correction: Heating curve generated on a different sample of same package style and construction with copper block heat sink showing impact of heat sink temperature rise and resultant data correction. The same grease as before was used for the thermal interface.The interface thermal resistance is discussed below. The cold plate thermal resistance is only of importance if, first, the heat is allowed to propagate well into the cold plate and, second, if the cold plate is not of sufficient capability to maintain a constant isothermal temperature at the package interface. If these conditions are satisfied, then the heating curve will show a plateau with a slightly positive slope, as indicated in Figure 6. In this case, a copper block approximately 5 cm square and 2.54 cm thick was placed on a different sample of the same package/chip combination. A thermocouple is placed approximately 0.13 mm from the block interface surface in the center of the block. The block thermal resistance, referred to as CP in this case, is computed as follows:

|

where: Tf = thermocouple value for a specific value of heating time

Ti = thermocouple value at temperature

equilibrium prior to the start of the test

PH = heating power applied during the test

When CP is subtracted from the measured results for each data point, the resultant curve shows the same zero-slope plateau obtained from a more ideal cold plate.

Measurement Problems

While overcoming many of the problems of the traditional JC measurement method, the thermal transient approach does introduce some of its own. First, while it is easy to see the thermal differences between different interface materials, determining the contribution of the best thermal interface material is not easy. In Figure 5 for example, the “grease” curve is the best (i.e., lowest) but there is no simple way to determine from the curve how much of the measured 2.96oC/W is actually

JC of the package and how much is due to the grease thermal interface material.The grease contribution to the thermal resistance can be calculated if the grease properties and the physical dimensions of the grease interface are known. The interface thermal resistance (

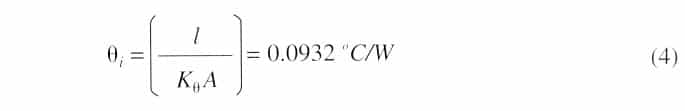

i) for this case is:

|

where: l = 0.00254 cm (thickness of grease)

A = 2.7258 cm2 (package surface contact area)

K = 0.01 W/K-cm (grease thermal conductivity)The

JC measured value could then be corrected for the

i value to produce

‘JC as follows:

‘JC =

JC –

i =2.96 – 0.0932 = 2.87 oC/W (5)In the example shown above, the impact of the interface material is relatively small; about 3% of the measurement value. For much larger measurement values, impact of the interface material can usually be ignored. However, the interface material thermal resistance can be a significant portion of smaller measurement values. One of the ways to overcome this problem is to make two sets of measurements; each with a different thickness of the same interface material. The difference in measurement values can then be attributed to the difference in interface material thickness assuming all other conditions remain the same. With this information in hand, the measured uJC can be appropriately corrected to determine

‘JC.Next, the electrical test method [see JESD51-1] used for determining junction temperature requires a reasonable change in temperature sensing diode junction voltage to accurately yield the junction temperature change. For most silicon semiconductor devices, a 10oC junction temperature change corresponds to a

VF of approximately 20 mV. Obtaining this change in TJ may require testing the sample at power levels higher than desired, thus introducing the question of thermal resistance power dependency. Usually power dependency is not an issue if the applied heating power is not excessive; typically not more than two or three times normal application power dissipation levels.Last, proper implementation of the thermal transient method requires a somewhat sophisticated test setup. The test sample junction temperature must be measured as a function of heating time, as per JESD51-1, over the heating time range of 1 millisecond to 10 seconds or more. If a non-ideal cold plate is used, then the cold plate temperature at the thermal interface must also be measured as function of heat time as well. The measured data then must be corrected as discussed above.

With these issues in mind, it is obvious that the interface or contact resistance between the package surface and the cold plate is often the biggest unknown in the measurement setup and the greatest measurement problem. Techniques still have to be more fully developed to accurately separate out the contribution of the interface thermal resistance from the desired package JC value.

Conclusion

The thermal transient method for JC measurements offers several advantages over the traditional approach of monitoring case temperature. First, it does not require mechanical modification to the package or cold plate to attach a thermocouple or to route the thermocouple leads away from the measuring point. Second, measurement variations caused by implementation skill level are greatly reduced because implementation is so easy. Third, as a result of relative simple implementation, the method lends itself to establishment of a measurement standard that will produce comparable data across multiple laboratories using the standard. Fourth, while some appreciable capital cost is required to set up the thermal transient test, the cost of making the measurement is relatively low, requires minimal package preparation and test time, and is non-intrusive. Fifth, this method allows more data to be collected without dedicating test samples to a particular measurement.

References

1. JESD51-1 Integrated Circuit Thermal Measurement Method – Electrical Test Method (Single Semiconductor Device)

2. JESD51-3 Low Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

3. JEDS51-9 Test Boards for Area Array Surface Mount Package Thermal Measurements

4. SEMI G30-88 Test Method for Junction-to-Case Thermal Resistance Measurements of Ceramic Packages

5. SEMI G43-87 Test Method for Junction-to-Case Thermal Resistance Measurements of Molded Plastic Packages

Note: These standards are available at the following web sites:

-

-

- http://www.thermengr.com (click on Standards Status)

- http://www.jedec.org

- http://www.semi.org

-

6. Blackburn, D.L. & Oettinger, F.F., Thermal Transient Response Measurements of Power Transistors, PESC 74 Record, 1974, pp. 140-148.

7. Siegal, Bernie, Elements of Device Thermal Characterization, Electronics Cooling, Vol. 1, No. 1, June 1995, pp. 18-20.

8. Dakuginow, S., Apides, R., & Lacap, E., Thermal Measurement Standards for ASIC Packaging, SEMICONDUCTOR INTERNATIONAL, June 1995, pp. 251-254.