Compact thermal modeling in electronics design

Sarang Shidore

Flomerics Inc

Introduction

The challenge of accurately predicting junction temperatures of IC components

in system-level CFD simulations has engaged the engineering community

for a number of years. The primary challenge has been that near-exact

physical models of such components (known as detailed thermal models,

or DTMs) are difficult to implement directly in system designs due to

the wide disparity in length scales involved, which results in large computational

inefficiencies. A compact thermal model (CTM) attempts to solve this problem

by taking a detailed model and extracting an abstracted, far less grid-intensive

representation that is still able to preserve accuracy in predicting the

temperatures at key points in the package, such as the junction.

The article will discuss the concept and utility of compact thermal models

and illustrate their use by designers in industry.

The Importance of Thermal Modeling

Simulation tools for the thermal modeling of semiconductor packages have

now become routine in most design processes. From early spreadsheet-type

tools that were in vogue a couple of decades ago, many designers now use

sophisticated FEA (Finite Element Analysis) or CFD (Computational Fluid

Dynamics) tools, and interface their mechanical CAD data directly into

their analysis. Modeling is seen as a necessary step, especially at the

early stages of thermal design, during which feasibility studies can narrow

the spectrum of possible design choices. Modeling is also used at later

stages of the design primarily for verification and design optimization.

Before we focus on the role of compact modeling in the thermal analysis

world, it is important to understand what a compact thermal model of a

semiconductor package is, and how it relates to the more fundamental detailed

thermal model.

What is a Detailed Thermal Model?

A DTM is a model that attempts to represent or reconstruct the physical

geometry of a package to the extent feasible. Thus the detailed model

will always look physically similar to the actual package geometry. Constructing

a DTM in a thermal analysis tool is aided by integration with mechanical

CAD data of the part. A properly constructed detailed model is, by definition,

Boundary Condition Independent (BCI); i.e., the model will accurately

predict the temperature at various points within the package (including

junction, case, and leads), regardless of the cooling environment in which

it is placed.

DTMs are suitable for use in the simulations of designs in which the

number of packages is few. For example, typical package thermal characterization

problems � such as calculations to extract qja

(junction-to-air thermal

resistance) or qjma (junction-to-movingair

thermal resistance) � fall under this category. However, DTMs are not

feasible for simulations of sub-systems or system-level computations,

which involve a large number of semiconductor packages. This is because

the computational resources required for solving such large problems would

be excessive if each package was represented by a DTM. These are precisely

the applications where a CTM should be used.

What is a Compact Thermal Model?

A CTM is a behavioral model that aims to accurately predict the temperature

of the package only at a few critical points � e.g., junction, case, and

leads � but does so using far less computational effort. A CTM is not

constructed by trying to mimic the geometry and material properties of

the actual component. It is rather an abstraction of the response of a

component to the environment it is placed in. Most CTM approaches use

a thermal resistor network to construct the model, analogous to an electrical

network that follows Ohm�s law. The most popular types of CTMs in use

today are two-resistor and DELPHI.

Two-Resistor CTM

A simple and widely-used CTM is a two-resistor model (Figure 1). It consists

of a thermal resistance from the junction to the board (junction-to-board

resistance, or qjb), and one from

junction to case (junction-to-case resistance, or qjc).

Both of these parameters are defined by the JEDEC industry standards committee

[1] as reference standards.

Figure 1. A two-resistor compact thermal model.

The junction-to-case resistance (qjc)

is normally derived from a “top cold plate test”, in which the

package is placed on a board with all sides insulated except the top surface.

A cold plate at a specified temperature is pressed against the top surface.

Hence, most of the power dissipated from the package leaves through its

top (isothermal) surface. The one-dimensional equivalent of Fourier’s

law is then applied to derive qjc.

Thus,

|

qjc = (Tj

– Tcld)/P |

(1) |

where Tj is the junction temperature and Tcld

is the temperature of the cold plate.

The junction-to-board resistance (qjb)

is derived by placing the package in a specially constructed harness known

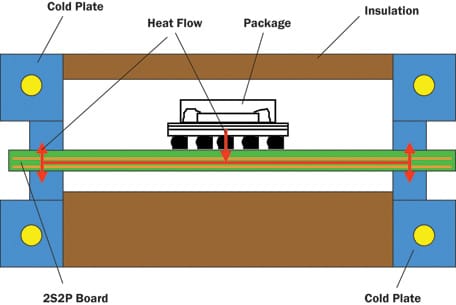

as the “ring cold plate.” The ring cold plate (Figure 2) fixture

consists of a 4-layer PCB (defined as in the reference document JESD51-7)

inserted between two cold plates. The cold plates are in the shape

of a ring. Thus heat travels from the package through some distance within

the board and then out of the fixture through the coolant fluid in the

cold plate.

Figure 2. Fixture for measuring qjb.

Rjb is calculated by using the one-dimensional version of

Fourier’s law:

|

qjbj

– Tb)/P |

(2) |

The board temperature (Tb) is taken as the temperature at

a point on the board surface located in the middle of the longest side

of the package, no more than 1 mm from the package edge for an area array

package and on the center lead foot for a surface-mount leaded package.

A two-resistor model has the following advantages:

- Its structure is simple and intuitive.

- It can be created from existing test data.

- It results in a significant increase in accuracy for prediction of

junction temperature compared to traditional single-resistor metrics,

such as qja.

DELPHI CTM

The challenge of compact modeling is to devise a generalized methodology

to generate a BCI CTM. To that end, the DELPHI [2] consortium, primarily

made up of a number of end-user companies, concluded an ambitious publicly

funded research project that led to the first comprehensive methodology

for the generation of BCI compact models. One of the key advantages of

the DELPHI methodology is that it is non-proprietary and vendor/tool independent.

The DELPHI project was followed by the SEED [3] project, in which component

suppliers evaluated the DELPHI methodology and found that it could be

used satisfactorily as a predictive tool for junction temperature.

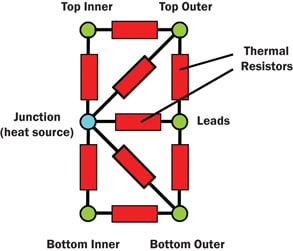

DELPHI compact models (Figure 3) comprise several thermal

resistors that connect a junction node (representing the die) to several

surface nodes. Thermal links are also allowed between the surface nodes

(shunt resistors).

Figure 3. A typical DELPHI compact model topology

The resistor network is derived from a step-by-step simulation

and statistical optimization process that minimizes the error in junction

temperature and heat flux over a wide spectrum of environments, such as

high/low conductivity PCB, bare package, package with heatsink, natural

convection cooling, and fan cooling. The end result is a CTM that provides

a predictive accuracy of junction temperature and major fluxes to within

10%; a major improvement over the accuracy of a two-resistor model.

Application Areas of Thermal Models

DTM

A properly constructed DTM will provide the best prediction accuracy for

all application environments. However, the computational efficiency of

DTMs is low. Therefore, they find the widest use among semiconductor manufacturers

for:

- Package characterization: This involves simulation of the DTM under

standard JEDEC environments for the extraction of standard metrics such

as qja, qjma,

qjb or CTMs. - New package design: This involves modification of existing designs

(e.g., by adding a slug or extra thermal vias) or the creation of a

new package design to meet product requirements.

DTMs, in general, are not suitable for use in board-level or system-level

design and exploring what-if scenarios that involve multiple packages.

Two-Resistor CTM

A two-resistor CTM can be used by system integrators and semiconductor

manufacturers to simulate designs with more than a single package on one

or multiple PCBs. Currently, two-resistor CTMs are the most widely used

among all CTMs.

Studies have indicated that the predictive accuracy for junction temperature

for two-resistor CTMs is about 30% or less. In cases where the heat is

predominantly going into the board or a heatsink, and when internal heat

spreading within the package is not large, the predictive accuracy will

be much higher. Two-resistor models also produce a higher accuracy for

parametrics; i.e., the difference in temperature between two variations

in cooling solutions for the package will tend to be more accurately predicted

than the absolute values of the temperatures.

Incidentally, it is important to note that the accuracy of prediction

of the case temperature is likely to be worse than the junction temperature,

especially in plastic or “glob-top” type of packages. This is

because the mold compound surface has a significant gradient of temperature,

and representing the top as a single node tends to average this temperature

out.

Thus it is advisable to use two-resistor models during the initial design

phase to predict approximate values of junction temperature and values

of the neighboring air temperature (local ambient). In later stages of

design, these models can be used to explore parametrics. Two-resistor

CTMs are sometimes the only option if the consumer of the model cannot

simulate a more complex CTM in their tools.Two-resistor CTMs should generally

be avoided for the prediction of case temperatures.

DELPHI CTM

High predictive accuracy, portability, and computational efficiency make

DELPHI CTMs the most suitable for wide dissemination from semiconductor

manufacturers to system integrators. Their BCI properties allow designers

to use them with a high degree of confidence for predicting junction temperature

and heat fluxes.

Typical junction temperature errors compared to the DTM do not exceed

5%. (It should be noted that small additional errors can be introduced

in this comparison because of the difference in the airside grid used

between the two simulations in practical situations.)

DELPHI CTMs are ideal for representing packages in board-level or system-level

simulations involving a large number of packages in which accurate temperature

and flux data is desired. If available, they should always be used in

preference to the two-resistor CTM.

Current State of Thermal Models in Industry

DTMs are currently used widely by semiconductor manufacturers for package

characterization and design.

Two-resistor CTMs have a long history of usage in aerospace/defense applications,

but in the last one or two decades this has extended to the other sectors

of the electronics industry. One continuing barrier to their universal

usage is the lack of èjb data from some semiconductor manufacturers.

It was a key vision of the DELPHI project that a supplier of electronics

components would not only deliver to its customer a product, but also

a CTM. When used in this manner, DELPHI CTMs have proven to be highly

successful in the accurate prediction of package thermal performance in

many design situations.

The drawback of DELPHI CTMs is the fact that not all semiconductor manufacturers

have made them available for their parts catalog. DELPHI CTMs still have

some way to go before they are adopted universally. However, this situation

is changing – one particular software vendor [4] reported that 35%

of all CTMs generated from their tools were DELPHI CTMs in 2006. Software

vendors too have a key responsibility in this regard to make the DELPHI

methodology widely available in their tools so that

industry can adopt them quickly.

Standardization procedures for both two-resistor and DELPHI CTMs are

in their advanced stages in the JEDEC industry standards committee. Work

is also underway for extending the CTM concept to transient situations,

i.e., Dynamic Compact Thermal Models (DCTM). A universal methodology for

this is not yet available, but several methods have been proposed by researchers.

Conclusions

Thermal modeling is now an integral part of the electronics design process.

In recent years, new thermal modeling methods have been proposed that

seek to predict temperatures and fluxes of packages with varying degrees

of accuracy and computational efficiency. These methods are being widely

used in the industry, although some important barriers to their universal

adoption remain. The JEDEC industry standards committee is engaged in

standardizing some of these methodologies.

Sarang Shidore

Flomerics Inc.

1106 Clayton Lane

Suite 525W

Austin, TX-78723

Tel: 512-420-9273, ext. 203

Fax: 512-420-9485

Email: sarang@flomerics.com

References

- 1. www.jedec.org

- Rosten H., Parry J., Lasance C. J. M. et al, “Final Report to

SEMI-THERM XIII on the

European-Funded Project DELPHI – The Development of Libraries and Physical

Models

for an Integrated Design Environment,” Proc. of the Thirteenth

IEEE SEMI-THERM

Symposium, Austin, TX USA, January 28-30, 1997. - Pape H.and Noebauer G., “Generation and Verification of Boundary

Condition Independent Compact Thermal Models for Active Components,”

According to the DELPHI/SEED Methods, Proc. of SEMITHERM XV, San Diego,

CA, pp. 201-211,1999,. - Flomerics Inc., Internal Report on Flopack Usage, 2006.