The increased integration density of electronic components and subsystems, including the nascent commercialization of 3D chip stack technology, has exacerbated the thermal management challenges facing electronic system developers. The sequential conductive and interfacial thermal resistances associated with the prevailing “remote cooling” paradigm in which heat must diffuse from the active regions on the chip to the displaced coolant, have resulted in only limited improvements in the overall junction-to-ambient thermal resistance of high-performance electronic systems during the past decade. These limitations of Commercial Off-The-Shelf (COTS) thermal packaging are undermining the cadence of Moore’s Law and leading to a growing number of products that fail to realize the inherent capability of their continuously improving materials and architecture. Moreover, continued application of this “remote cooling” paradigm, has resulted in electronic systems in which the thermal management hardware accounts for a large fraction of the system volume, weight, and cost and undermines efforts to transfer emerging components to small form-factor applications.

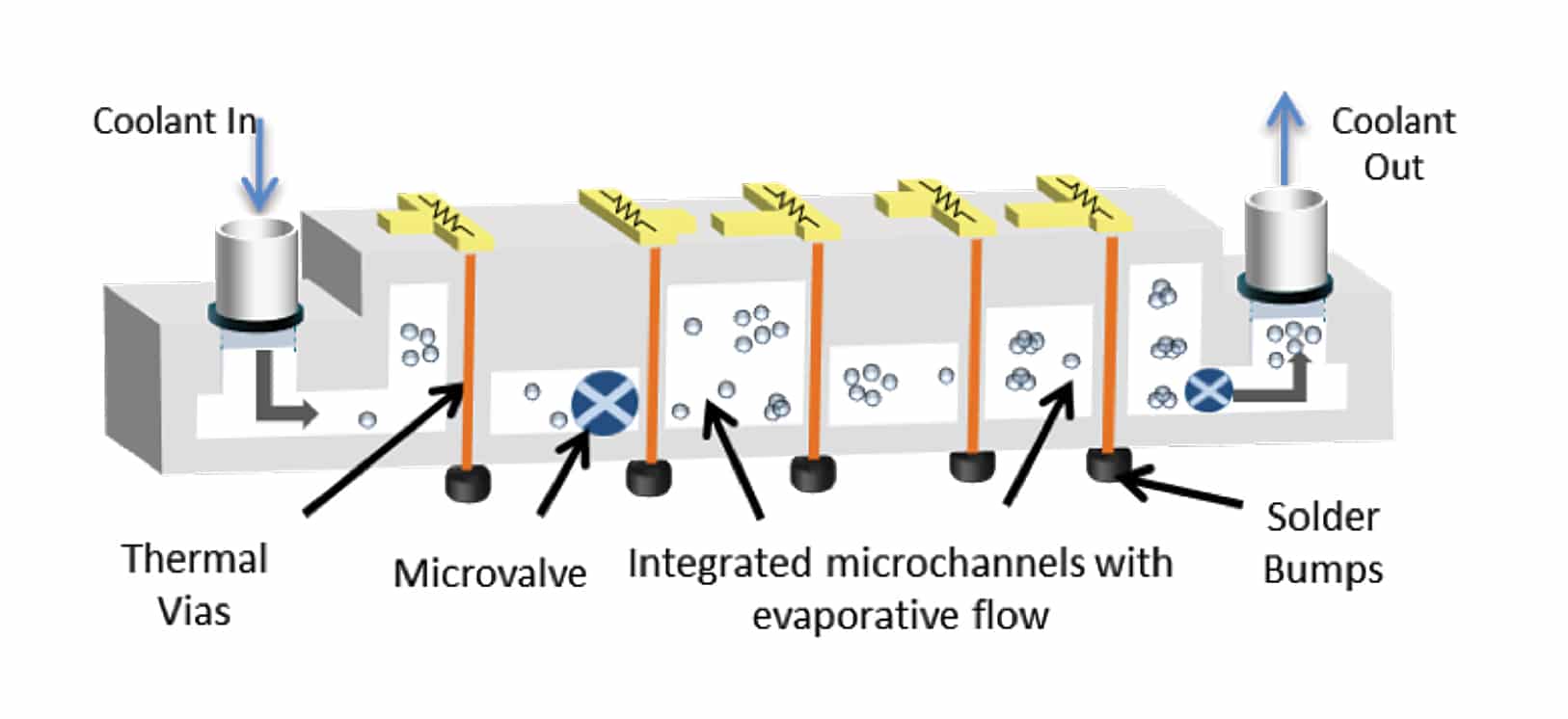

To overcome these limitations and remove a significant barrier to continued Moore’s Law progression in electronic components and systems, it is essential to implement aggressive thermal management techniques that directly cool the heat generation sites in the chip, substrate, and/or package. The development and implementation of such “Gen-3” embedded thermal management technology, following on the Gen-1 air-conditioning approaches of the early years and the decades-long commitment to the Gen-2 “remote cooling” paradigm, is the focus of the current DARPA Intra/Inter Chip Enhanced Cooling (ICECool) thermal packaging program. Launched in 2013, ICECool aims to develop and demonstrate “embedded cooling” techniques capable of removing kW/cm2 chip heat fluxes and kW/cm3 chip stack heat densities, while suppressing the temperature rise of multi-kW/cm2 sub-mm hot spots [1,2]. The ICECool program is composed of two thrusts: a 3-year ICECool Fundamentals effort, involving several university teams which are developing embedded cooling building blocks and modeling tools, and a 2.5-year ICECool Applications effort, led by several aerospace performers and culminating in functional electronic demonstration modules. ICECool performers are pursuing the creation of a rich micro/nano grid of thermal interconnects, using high thermal conductivity, as well as thermoelectric, materials to link on-chip hot spots to microfluidically-cooled microchannels. Such intra/inter chip enhanced cooling approaches are required to be compatible with the materials, fabrication procedures, and thermal management needs of homogeneous and heterogeneous integration in 3D chip stacks, 2.5D constructs, and planar arrays. A conceptual ICECool device is shown in Figure 1.

An intrachip approach would involve fabricating micropores and microchannels directly into the chip [3,4] while an interchip approach would involve utilizing the microgap between chips in three-dimensional stacks [5,6], as the cooling channel. In addition to the inclusion of an appropriate grid of passive and/or active thermal interconnects, it is expected that a combination of intrachip and interchip approaches, linked with thru-silicon and/or “blind” micropores, will confer added thermal management functionality. These microchannels and/or micropores will be integrated into a fluid distribution network, delivering chilled fluid to the chip or package and extracting a mixture of heated liquid and vapor to be transported to the ambiently-cooled radiator.

Some 30 years of thermofluid and microfabrication R&D, driven initially by the publication of the Tuckerman & Pease microchannel cooler paper in 1981 [1] and more recently by compact heat exchanger and biofluidic applications [7,8], has created the scientific and engineering foundation for the aggressive implementation of the “embedded cooling” paradigm. Nevertheless, substantial development and modeling challenges must be overcome if Gen-3 techniques are to supplant the current “remote cooling” paradigm. Successful completion of the DARPA ICECool program requires overcoming multiple microfabrication, thermofluid, and design challenges, including:

- Subtractive and additive microfabrication in silicon, silicon carbide, and synthetic diamond of high aspect ratio, thin-walled microchannels and high aspect ratio micropores; low thermal boundary resistance, high thermal conductivity thermal interconnect grids; on-chip, high power factor, high COP thin-film thermoelectric coolers; and hermetic attachment of liquid supply and liquid/vapor removal tubes.

- Convective and evaporative thermofluid transport in microchannels and micropores– removal of 1 kW/cm2 chip heat fluxes with 2-5 kW/cm2 sub-millimeter “hot spots”; low pumping power liquid-vapor manifolds with Coefficients-of-Performance (CoP) between 20 and 30; high-exit-quality, greater than 90%, evaporative flows without flow instabilities and/or local dryout; and high fidelity thermofluid models for single- and two-phase flow in microchannels, microgaps, and micropores.

- Thermal and electrical co-design which moves progressively from passive, thermally-informed designs, which recognize the impact of temperature on functional performance, to active thermal co-design which places functional paths and blocks in the most favorable locations on the chip, to fully-integrated co-design which deals with the impact of microfluidic channels and thermal interconnects on the electrical design and placement of electrical devices and cells, to mature designs that interactively balance the use of resources to optimize layout for energy consumption and functional performance.

- Physics of Failure models that address the failure mechanisms and reliability of the Gen-3 thermal management components, including erosion and corrosion in microchannels, microgaps, and micropores; failure modes induced in the electrically active areas of the chip and/or substrate; and the impact of microfabrication and embedded cooling operation on the structural integrity and stress profile of the microchanneled substrate (intrachip) and/or the chip-to-chip bonding (interchip).

Successful development and implementation of this Gen-3 thermal packaging paradigm would place thermal management on an equal footing with functional design and power delivery, transforming electronic system architecture and unleashing the power of nanofeatured device technology, while overcoming the SWaP (size, weight, and power consumption) bottleneck encountered by many advanced electronic systems. After decades of mere “problem solving” with Gen-1 (HVAC) and Gen-2 (spreaders, heat sinks, and TIMs) thermal management technology, it is expected that widespread adoption of Gen-3 “embedded cooling” techniques will provide a significant performance multiplier for advanced electronic components.

References

- Intrachip/Interchip Enhanced Cooling Fundamentals (ICECool Fun), DARPA BAA 12-50, Posted 7 June 2012.

- ICECool Applications (ICECool Apps), DARPA BAA 13-21, Posted 6 February 2013.

- D.B. Tuckerman and R.F.W. Pease. “High-performance heat sinking for VLSI.” IEEE Electron Device Letters, vol. 2, no. 5, pp. 126–129, 1981.

- L.P. Yarin, A. Mosyak and G. Hetsroni. Fluid Flow, Heat Transfer, and Boiling in Micro-Channels. Springer, Berlin, 2009.

- A. Bar-Cohen and K.J.L. Geisler. “Cooling the Electronic Brain.” Mechanical Engineering, pp. 38–41, April 2011

- A. Bar-Cohen, J. Sheehan and E. Rahim. ”Two-Phase Thermal Transport in Microgap Channels – Theory, Experimental Results, and Predictive Relations.” Microgravity Science and Technology, pp. 1–15, Sept. 2011.

- S.Garimella, T. Harirchian, Microchannel Heat Sinks for Electronics Cooling, Volume 1, Encyclopedia of Thermal Packaging, 2013, WSPC, Singapore

- L.P. Yarin, A. Mosyak, H. Hetsroni, Fluid Flow, Heat Transfer, and Boiling in Micro-Channels, 2009, Spring-Verlag, Berlin

Disclaimer: The views, opinions, and/or findings contained in this article/presentation are those of the author/presenter and should not be interpreted as representing the official views or policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the Department of Defense.

Distribution Statement A, Approved for Public Release, Distribution Unlimited.