Three dimensional (3D) integration is considered a very promising technology for integrated circuit design [1]. It offers numerous opportunities to designers looking for more cost-effective system chip solutions. It allows further decrease in the form factor of today’s systems and eases the interconnect performance limitation since the components are integrated on top of each other instead of side-by-side, resulting in shorter interconnect lengths. Furthermore, it makes it possible to interconnect multiple heterogeneous chips, and with much higher I/O density than in today’s packaging solutions [2]. Thermal management issues in these 3D stacks are considered to be one of the main challenges for 3D integration [3]. The use of polymer adhesives with low thermal conductivity, the vertical integrations of the chips and the reduced thermal spreading due to aggressively thinned dies cause these thermal management issues. The presence of interconnection structures, back end of line (BEOL), redistribution layers (RDL) and through-Si vias (TSVs) increases the complexity of the conductive heat transfer paths in a 3D stack. To understand the effect of these TSVs and inter-tier connections, a detailed analysis of the heat transfer in 3D stacks, including the TSVs is needed.

This article focuses on the hot spot power dissipation in two-die stacks. The impact of TSVs and the Cu-Cu bonding on the temperature profile of the top and bottom die is studied by using dedicated test structures consisting of integrated thermal heaters and temperature sensors. Die stacks including these structures are used to calibrate the thermal finite element modeling of the temperature distribution in the 3D stack.

Thermal test vehicle for 3D stacks

Dedicated test chips with integrated thermal structures are used to mimic power dissipation of a real chip and, at the same time, monitor the temperature at different locations in the stack. The 5×5 mm2 top die is thinned down to 25 µm, to expose the 5µm TSVs at the backside; the top die is then stacked face-up on the 8×8 mm2 bottom dies contained in the full thickness (725µm) landing wafer using Cu-Cu thermo-compression bonding [4] resulting in a typical stand-off height of 700 nm to 1 µm between the chips, shown in Figure 1. Cu meander heaters in the BEOL with sizes of 50×50 and 100×100 µm² respectively are used to dissipate power, and integrated diodes in both top and bottom die are used as temperature sensors. The temperature sensitivity of the diode is -2 mV/ºC in the temperature range of 20 to 80 ºC. Using a low current of 10 µA, power dissipation of the diode itself is negligible with respect to the power dissipated in the heaters. At the position of each heater, a set of 5 diodes at different distances (0, 60, 80, 120 and 160 µm respectively) from the hot spot center is added to both the top and bottom chip in order to capture the local temperature peak, and to monitor the vertical heat conduction in the stack. Furthermore, different TSV densities are used in the test chip, locally below the heaters to characterize their ability to enhance the heat transfer: a reference structure without TSVs, an array of 7×7 and 11×11 TSVs. Figure 2(a) shows a schematic representation of the cross-section of the test structures. In Figure 2(b), a detail of the layout at the location of a test structure is shown to reveal the location of the heater, diodes and TSV array.

Figure 3 shows a schematic cross section and a picture of the 2-level PCB that is used to provide the connections to the heaters and diodes. Four-point measurements are used both for the power dissipation and the temperature measurements. A Cu plate is glued to the backside of the PCB while the backside of the Cu plate is attached to a temperature-controlled, water-cooled heat sink. The chip stack under test is mounted on this Cu plate using a thermal interface material (TIM) and the chip stack is electrically connected to the PCB by wirebonds. The top side of the chip stack is thermally insulated, forcing the heat generated in the top die of the stack to be removed through the bottom side, to the heat sink.

Thermal modeling

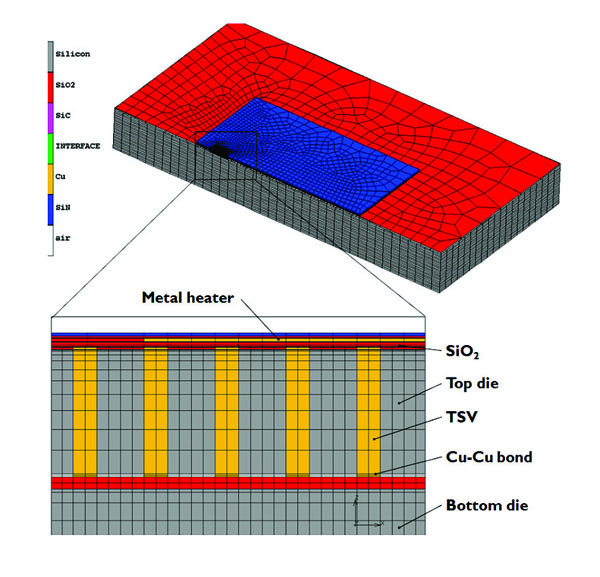

Different thermal modeling approaches can be used to predict the thermal impact of TSVs and the Cu-Cu bonding in 3D-ICs at different stages of the design process. These approaches range from fast solving first order thermal calculations in the initial stage of the design [5,6], up to a detailed fine grain simulation including all layout details for the final verification of the design [7,8]. The FEM approach provides sufficient detail by allowing to include individual TSVs in the thermal analysis, while the computational time is sufficiently low to allow transient analysis. A parameterized finite element model representing the stack has been constructed using a commercial software package [9]. Figure 4 shows a cross section of the model of the two-die stack. As boundary conditions, a heat flux represents the power dissipation in metal meander heaters. At the bottom of the die stack, an equivalent thermal resistance mimics the connection of the die stack to the Cu plate. The temperature distribution in the stack has been studied for the 6 different test structures on the test chip.

Thermal comparison of 2D versus 3D integration

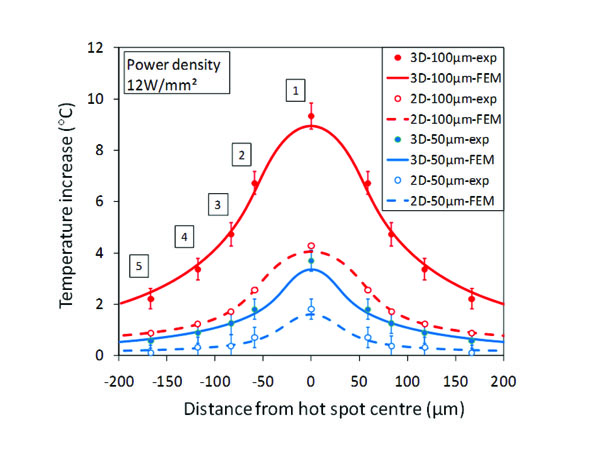

The 2D reference case is a full thickness die containing the integrated heaters and temperature sensors, whereas in the 3D case, the heaters are in the thinned top die, stacked on top of a full thickness bottom die. Figure 5 shows the experimental and modeling results for the temperature profiles in case of the test structure without TSVs for a power density of 12 W/mm2 in the hot spots for the 2D and 3D case. For the experimental results, the error bars for the 95% confidence intervals based on the student’s t-distribution are shown for 10 die stacks. The local temperature increase in the case of the 3D configuration is two to three times higher compared to the 2D reference case. Besides an increase in peak temperature, also a broadening of the temperature peak can be observed. The normalized peak temperature is 82 K/W and 125 K/W for the 100×100 µm2 and 50×50 µm² respectively. The measurement results indicate that the diodes are capable of capturing the local temperature peak below the hot spots. Furthermore, from this figure a good agreement between the modeling and experiments is observed.

Thermal impact of TSVs

The simulations predict a local temperature reduction for an increasing TSV density compared to the no TSV case. A reduction of the local temperature increase of 7% and 20% is predicted for the 7×7 array and 11×11 array respectively. This is shown by the dashed lines in Figure 6(a) for the 100µm heater. However, a temperature increase (7×7 array) and a less than predicted temperature reduction (11×11 array) have instead been observed experimentally in all 10 chips. A detailed FIB-SEM analysis of the cross-section of the die-die interface revealed non-connected TSV in the outer ring of the arrays, slight variations in the stand-off height and non-uniform distribution of the polymer adhesive. The finite element model has been updated by taking into account these deviations from the designed geometry. The updated simulation results are able to correctly predict the expected impact of TSVs density (solid lines in Figure 6a). This analysis shows that the thermal impact of the die-die interface (adhesive, metal bond or voids) is at least as important as the impact of the TSVs for these stacks with a stand-off height from 700nm to 1µm. In the case of Cu or CuSn microbumps, the stand-off height is typically in the order of a few tens of µm and a larger thermal impact of the vertical die-die connection compared to the impact of TSVs is expected.

A transient analysis has been performed using a temporal resolution of 10 µs, which is sufficient to capture the fast temperature rise. From these measurements, the time constants for the temperature response are 100 µs and 200 µs for the top and bottom die, respectively. This is much faster than the transient response for uniform heating, for which a time constant of about 1s is typical. Figure 6(b) shows the comparison between the simulations results from the updated model and the experiments for the 100×100 µm2 heater. For the 7×7 array a reduced vertical heat transfer (higher top die temperature, lower bottom die temperature) is observed. Due to the presence of non-connected TSVs, locally a larger fraction of the heat travels horizontally away from the heat source before travelling vertically towards the heat sink. The negative thermal effect of the non-connected TSVs dominates the positive effect of the added vertical connection with high thermal conductivity whereas in the case of the 11×11 array the positive effect of the high density array of TSVs is larger than the negative impact of the non-connected TSVs.

The calibrated thermal models for the two die stack are integrated [10] in an early physical design exploration flow, a.k.a. PathFinding flow [11]. This coupling of thermal and mechanical models to the design flow allows optimization of the design of stacked chips, as well as fine tuning stacking technology options, including TSV and microbump layout, for minimizing thermal and mechanical stress. The purpose of the PathFinding is to validate product ideas for 3D, including the thermal and mechanical consequences, in the early phases of system design, before any large investments are needed.

Concluding remarks

This article presents the thermal impact of TSVs and Cu-Cu bonding in 3D-ICs using finite element simulation and dedicated thermal test chips with integrated hot spot heaters, sensors and TSVs. Hot spot power dissipation results in significantly higher temperatures in 3D stacked chips compared to the same power dissipation in single 2D chips. This temperature increase is mainly due to the reduced thermal spreading in the thinned dies on the one hand, and to the use of adhesives with low thermal conductivity for the vertical integration of the chips on the other hand. Therefore, a detailed thermal analysis of the packaged 3D-IC is required and the conventional cooling solution used for the 2D chip might not be sufficient for the cooling of the 3D chip package. To limit the temperature increase in 3D-ICs, too thin chips should be avoided. Indeed, the thinner the silicon substrate, the higher the thermal spreading resistance is in the case of hot spots [12]. Simulations, used to extrapolate the experimental results of the 25 µm thick test chip for other thickness values, show that a minimum die thickness of 50 µm is required to deal with the local hot spots on the presented thermal test chip.

The study on the impact of TSVs on the temperature profile in the test chips shows that the thermal impact of the presence of the die-die connections, such as Cu or CuSn microbumps or direct Cu-Cu bonds, is more important than the presence of the TSVs itself. The Cu TSVs with high thermal conductivity (390 W/mK) are inserted in the Si, which is well conductive (150 W/mK at room temperature and120 W/mK at the operating temperature). Typical conductivity values for the underfill materials are 0.2 W/mK for unfilled underfills and 0.3-0.4 W/mK for filled underfills, depending on the amount and type of filler particles. The difference in thermal conductivity between the metallic bonds and the adhesive material is thus two orders of magnitude. As a result, well placed dummy microbumps, rather than dummy TSVs, can be used to increase the effective thermal conductivity and to reduce the temperature increase in a 3D stack.

References

[1] Chanchani, R. “3D Integration Technologies – An Overview,” in Materials for Advanced Packaging edited by D. Lu, C.P. Wong, Springer (2009), pp. 1-50.

[2] Beyne, E. “Through-Silicon via Technology for 3D IC,” in Ultra-thin Chip Technology and Applications, edited by J.N. Burghartz, Springer (2011).

[3] Brunschwiler, T.; Michel, B. “Thermal Management of Vertically Integrated Packages,” in Handbook of 3D Integration: Technology and Applications of 3D Integrated Circuits, edited by P. Garrou, C. Bower and P. Ramm. Wiley-VCH Verlag GmbH (Weinheim, 2008) Vol. 2, Part IV, pp. 635-649.

[4] Swinnen, B.; Jourdain, A. ; De Moor, P. ; Beyne E. Chapter in Wafer Level 3-D ICs Process Technology; edited by S. Tan, R.J. Gutmann, and L.R. Reif (Eds), Springer, 2008.

[5] Sridhar, A.; Raj, A.; Vincenzi, A.; Ruggiero, M.; Brunschwiler, T.; Atienza. D. “3D-ICE: Fast compact transient thermal modeling for 3D-ICs with inter-tier liquid cooling,” ICCAD 2010, San Jose, CA, USA.

[6] Torregiani, C.; Oprins, H.; Vandevelde, B.; Beyne, E.; De Wolf, I. “Compact thermal modeling of hot spots in advanced 3D-stacked structures,” Proc. EPTC 2009, pp. 131-136.

[7] Melamed, S.; Thorolfsson, T.; Srinivasan, A.; Cheng, E.; Franzon, P.; Davis, W.R. “Investigation of tier-swapping to improve the thermal profile of memory-on-logic 3DICs,” Therminic 2010, Barcelona, Spain, 6-8 Oct. 2010.

[8] Oprins, H.; Srinivasan, A.; Cupak, M.; Cherman, V.; Torregiani, C.; Stucchi, M.; Vandevelde, B.; Van der Plas, G.; Marchal, P. and Cheng, E. “Fine grain thermal modelling and experimental validation of 3D-ICs,” Microelectronics Journal, Vol. 42 (4), April 2011, pp. 572-578.

[9] MSC.Marc, URL: http://www.mscsoftware.com/Products/CAE-Tools/Marc.aspx

[10] Milojevic, D.; Oprins, H.; Ryckaert, J.; Marchal, P.; Van der Plas, G. “DRAM-on-logic Stack – Calibrated thermal and mechanical models integrated into PathFinding flow,” IEEE Custom Integrated Circuits Conference (CICC), 2011.

[11] Milojevic, D.; Varadarajan, R.; Seynhaeve, D.; Marchal, P. “PathFinding and TechTuning,” in Three Dimensional System Integration, Springer (2011), pp. 137 – 186.

[12] Lasance, C. “Thermal Facts & Fairy Tales: Heat Spreading Revisited,” Electronics Cooling, March 2012.