Electronics industry needs for improved performance of thermal interface materials (TIMs) are driving continued reductions in thermal resistance. These reductions are being achieved with materials that become liquidous or near-liquidous at predictable operating temperatures, with extremely high thermal conductivity filler materials, or with both. Metallic alloys with low melting points, polymeric materials with the ability to change phase at a given temperature, and metallic particles and spheres as fillers in phasechange carriers and thermal greases are all methods of attaining both minimum material thickness at a given temperature and pressure. This combines with the ability of such materials to flow and fill surface asperities and develop final material thicknesses that are determined by the largest filler particle size. These types of materials enable reductions in thermal resistance between two surfaces at the lowest values achievable before moving to a solder material.

Solder materials, both with and without reflow processes, have historically been utilized for power semiconductor and RF semiconductor packages and are now also used in certain highvolume integrated circuit packages. The use of so-called solder shims as a “dry joint” solder thermal interface material (STIM) is one of several principal TIM materials used for RF devices in wireless base station power amplifiers and other RF device applications. Competing materials traditionally included silicone-filled thermal greases and, more recently, phase-change polymeric materials. Use of metallic and solder TIMs is an established practice in electronics packaging, largely in power semiconductor applications. Development of additional high-performance TIM materials containing low melting point metal alloys and other constituents provide reduced thermal resistances. However, these materials must also be evaluated for their potential for electrochemical reaction with other package materials, humidity effects, and other characteristics not traditionally associated with TIM material selection.

In processor packages, commodity microprocessor manufacturers replaced ceramic substrates with organic substrates 12 years ago due to, among other reasons, lower total packaging costs. The traditional industry model for these products has required the system-level customer to manage the thermal management design. Increasing power dissipation for processors has been documented in numerous presentations and industry roadmaps [1]. As power dissipation and heat flux values have risen over succeeding generations of microprocessors, substantially more attention has been focused on development of new thermal interface materials and improved package materials for lids and heat spreader components. Continuing development of new and increasingly more specialized TIM materials requires greater understanding of the nature of those specialized characteristics and the potential represented for electrochemical interaction with other materials, changed performance metrics, differing handling and storage and application requirements, and similar factors that impact successful package and system design.

High-volume commodity microprocessors are only one application for TIM materials. Hundreds of TIM materials manufactured by many companies serve scores of current market segments with very different performance, application, and cost requirements. Demands for these materials will continue and grow with increases in market production volumes. While calls for improvements such as “10X improvement in TIM materials” will resonate well as a demand for action, an important missing component of such a statement is the metric by which to judge success.

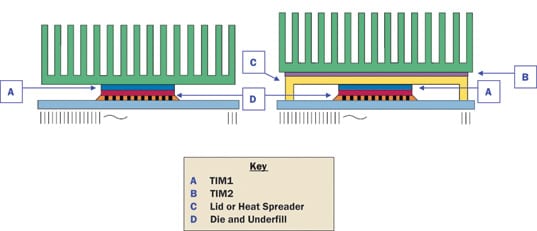

It is necessary to describe the base material and performance for which a tenfold improvement is desired: is it to be polymeric materials, metallic alloys, or reflowed solder? The goal of such quests is to develop materials that lower package thermal resistance (“TIM1,” between the die and lid, shown in Figure 1) and that lower overall package-to-case thermal resistance (“TIM2,” between the surface of the package lid and the base surface of the thermal solution employed).

Figure 1. Typical IC package construction identifying TIM1 and TIM2

placement for bare die package (left) and lidded package (right).

The increasing specialization of needs in the TIM market also has brought forth new materials with differing characteristics. A recent article illustrated the so-called “pull-out” problem associated with commodity microprocessors, wherein phasechange TIMs exhibit high adhesion after the transition temperature has been reached, followed by resolidification [2]. This characteristic has certain effects on shock testing and processor rework, and yet phase-change TIMs have been very successfully used in processor and power semiconductor applications across many industry segments.

This example illustrates that what is perceived as a negative characteristic in one application with specialized requirements may, in fact, have no impact in other applications. The highest single-unit volume application worldwide for TIM2 materials of any type is for a processor application for a major microprocessor manufacturer, a fact that further compounds the mystery of specialized TIM material applications for the practicing original equipment manufacturer (OEM) thermal engineer.

Much industry and academic attention is focused on new material development for extremely high performance levels, including solders and other metals and those containing structured carbon nanotube (CNT) arrays. Some developments include work to combine materials such as growth of structured CNT arrays transferred onto a solder-coated copper foil substrate or directly onto a coated package lid or baseplate [3]. Excellent discussions have appeared recently on the use of solder materials, in particular indium and indium alloys, in relation to package thermal resistance improvements for high-volume microprocessors [4].

Increasing power dissipation, heat flux, and product life requirements for power semiconductors for traction, hybrid vehicle powertrains, laser diode arrays, and other applications is leading to further evaluation of engineered thermal materials (ETMs) with specific coefficient of thermal expansion (CTE) and thermal conductivity values, and driving new requirements for further development of new package thermal materials to improve thermal performance and overall reliability. These requirements are now duplicated in efforts to obtain significantly higher thermal conductivity with selective CTE values for lid, heat spreader, and baseplate components for server processors and advanced graphics processors, in combination with direct die solder attach and other forms of metallic TIMs.

Traditional TIM solutions have been directed at implementing filler materials with high bulk thermal conductivity in various forms into polymer compounds. Maintaining a minimum material thickness in-situ [often referred to as minimum bond line thickness (BLT)] is critically important in practice, as is obtaining improvements in surface wetting to reduce interfacial resistance. These approaches raise new issues in material selection for thermal and packaging engineers. Whether this can be done at cost levels consistent with industry practice for a very broad range of electronics applications has yet to be determined. A further need is better industry education on the methods employed for testing TIM material performance [5].

Calls for development of improved TIM materials for application within commodity microprocessor products as a TIM1 and externally as a TIM2 should also be measured against a reexamination of the use of organic substrates for these same packages. While the lower cost of an organic substrate is important to the semiconductor manufacturer, the use of such a material also in some instances may limit the clamping force applied, an important determinant of performance of any TIM material. Clamping force can also be one determinant of package electrical interconnect performance.

Although transferring the cost burden of the thermal solution to the OEM is advantageous to the semiconductor manufacturer, the increasing power dissipation values indicate a rapidly increasing total cost burden for improved total thermal solution performance at the OEM level. This may in fact drive demands for improvements in TIM materials that are unrealistic. The cost of improved materials is not simply the cost of the TIM, which is rising as performance increases require the use of higher thermal conductivity fillers and consideration of solders and higher cost materials.

The noncommodity processor manufacturers have continued to utilize ceramic substrates, although at higher cost. Ceramic substrates may in certain (though not all) instances allow higher clamping forces, improved electrical performance, improved substrate flatness control (resulting in thinner lid edge seal adhesive and thinner initial TIM1 BLT). Use of matched coefficient of thermal expansion (CTE) materials with higher thermal conductivities for lids and heat spreaders and other attributes yields improved package performance. The use of a ceramic substrate and a lid with a CTE matched to the ceramic substrate allows use of a more rigid TIM, resulting in improved thermal resistance with either reduced TIM thickness or more highly filled TIM materials. Package design decisions, packaging materials, and engineered thermal materials (both lid or baseplate materials with specific CTE values and advanced TIM1 and TIM2 materials) offer the ability to gain further reductions in overall package thermal resistance.

Lid, baseplate, and other package heat spreader material developments that offer significantly higher thermal conductivity, combined with specified coefficient of thermal expansion values for direct solder joining (or brazing, commonly used for RF devices) to various packaging materials are also receiving much attention. These relatively stiff package component materials are intended to replace aluminum, copper, tungsten-copper and similar metal alloys, and other well-defined basic packaging materials for which manufacturing and metallization and utilization procedures are well understood.

Utilization of CVD diamond deposition on a thinned die to achieve first-level heat spreading in intimate contact with the localized high heat flux of die hot spots may also represent a change in the overall package resistance scheme, with or without metallization for wetting. Use of extremely high thermal conductivity materials such as carbon/copper and copper/diamond structures as heat spreaders and lids without corresponding implementation of metallic forms of TIM materials would sharply reduce the value of the engineered highly conductive spreader or integrated heat spreading layer.

The intersection of these two development areas (advanced TIMs that are metallic or employ metallic constituents and advanced composite packaging materials) requires new and greater focus to identify how these two types of materials may interact. Specifically, the identification of potential failure mechanisms from mechanical and electrochemical interaction (and often combined with thermal cycling or high humidity) is an area needing heightened focus for the packaging engineer who may not be a materials scientist. Broader awareness of the implications of these interactions can also be useful for developing solutions in integrated circuit, processor, RF, power LED, hybrid vehicle powertrain drive electronics, and military and automotive power supply applications of advanced TIM materials.

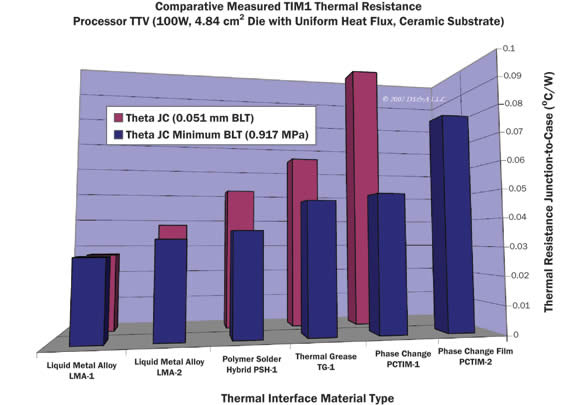

Comparative testing within one IC test package of the highest performing types of TIM materials was conducted to illustrate progressive improvements across a number of different classes of advanced TIM materials, as shown in Figure 2. In-situ testing of this type clearly depicts the performance improvements available within a thermal test vehicle that corresponds to a specific package and semiconductor device, including the relevant die material, die crowning (i.e., relative flatness or lack thereof) and surface texture, lid material and finish and flatness, clamping force, any metallizations, and other factors such as relative wettability of each contacting material.

Figure 2. Comparative thermal resistance values for several classes of advanced

thermal interface materials. Data shown was collected as thermal resistance, junction-to-case qJC), utilizing a Thermal Test Vehicle for an advanced processor.

Two tests for each material, utilizing (a) bond line thickness (BLT) of 0.051 mm (0.002”) and (b) minimum BLT under pressure, indicate the performance change achievable as pressure is increased and thickness minimized. Materials illustrated are commercial materials (in production or sampling for evaluation), including metal alloy-containing TIMs which do not require solder reflow temperatures.

Figure 2 shows data resulting from testing of the highest performance TIM materials currently available or in initial stages of sampling for commercial release, excluding solders and solder TIMs. This data describes thermal resistance (junction-to-case) as tested in a current processor package utilizing a ceramic substrate and two TIM1 bond line thicknesses: 0.051 mm (0.002”, predetermined by the use of shims) and an end-of-line minimum bond-line thickness at a higher pressure (0.917 MPa or 133 PSI) that is typical for commodity microprocessor applications. This data illustrates, in an in-situ processor thermal test vehicle, how very recently developed commercial TIM1 materials perform in comparative testing.

A summary of thermal performance data and an outline of the manufacturing process utilized for indium as a solder TIM (or STIM) as a TIM1 by a commodity microprocessor manufacturer are available in the literature [6].

Summary

Market drivers for increased overall thermal performance for semiconductor assemblies are increasingly leading to development of TIM materials with greater specialization in form factor, cost, thickness and thermal conductivity, compliancy, reliability targets, application parameters, automated placement, handling and storage capabilities, operating temperature ranges, and other distinct characteristics. Demands for improved thermal conductivity and package reliability lead to transition from polymeric and traditional thermal greases to similar materials with metallic constituents and ultimately to solder-like and reflow solder applications for TIMs. Increasingly specialized TIM materials are also utilized in packaging applications where compatibility with other packaging materials is growing in importance, where thermal cycling, moisture, electrochemical reactions, and other factors must be taken into account.

The semiconductor packaging engineer and the system thermal engineer responsible for a reliable package and thermal solution need to be aware of the increasing complexities that increasing materials specialization represents for thermal interface materials and engineered thermal materials and underfills, solders, ceramic and organic substrates, and other package components.

References

- International Technology Roadmap for Semiconductors, 2005 and 2006 editions:

www.itrs.net/Links/2005ITRS/Home2005.htm

www.itrs.net/Links/2006Update/ - Stern, M., Kearns, D., Ong, B., “Adhesion of Thermal Interface Materials for CPU Heat Sinks, an Overlooked Issue,” ElectronicsCooling, Vol. 13, No. 1, pp. 28–29, February 2007.

- Zhu, L., Wong, C., “Well-Aligned Carbon Nanotubes for Thermal Interface Material Applications,” Thermal Interface Materials Symposium, Georgia Institute of Technology, Atlanta, Georgia, September 27, 2006 (unpublished).

- Hua, F., Deppisch, C., Fitzgerald, T., “Indium as Thermal Interface Material for High Power Devices,” Advancing Microelectronics, International Microelectronics and Packaging Society, pp. 16–17, July–August 2006.

- Lasance, C., Murray, C., Saums, D., Rencz, M., “Challenges in Thermal Interface Material Testing,” Proceedings of Semi-Therm 22 Conference, Dallas, Texas, March 15-17, 2006.

- Rauch, R., “Test Methods for Characterizing the Thermal Transmission Properties of Phase-Change Thermal Interface Materials,” ElectronicsCooling, November 2000.