# **Belectronics COOLING**

#### FEATURED IN THIS EDITION

20 THERMAL MANAGEMENT OF CHIP-ON-BOARD LED SYSTEMS AND THEIR AGING RESPONSE TO CYCLIC POWER

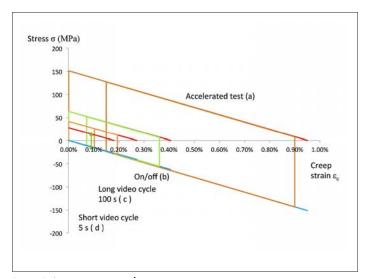

26 SOLDER JOINT LIFETIME OF RAPIDLY CYCLED LED COMPONENTS

30 MECHANICAL CYCLING RELIABILITY TESTING OF TIMS DEVELOPED SPECIFICALLY FOR SEMICONDUCTOR TEST

#### **6 CALCULATION CORNER**

APPLICATION OF TRANSIENT THERMAL METHODS TO MOISTURE DIFFUSION CALCULATIONS, PART I

**12 THERMAL FACTS & FAIRY TALES** FAIRY TALES ABOUT HEAT SINK PERFORMANCE CALCULATIONS

> 16 STATISTICS CORNER PROBABILITY

© Copyright 2020 Electronics Cooling

# **Liquid Cooling Solutions**

Professionally designed, built and tested to withstand harsh environments

- High performance Coolant Distribution Unit (CDU)

- Impinging cold plate design with lower pressure drop

- Broad range of testing equipment to ensure product quality and performance

- Micro-channel cold plate block designs

- Liquid direct cooling for memory DIMMs

- High-grade tubing with low permeation, high-pressure capacity and small bending radii achievable

- Hot-swappable quick-disconnect capability for dry disconnect

#### www.delta-fan.com | dcfansales.us@deltaww.com

# MAY 12, 2020 **thermal**<sup>LIVE</sup> BOOTCAMP **ONLINE EVENT**

#### Thermal LIVE Bootcamp: Thermal Management Training Course

Introducing Thermal LIVE Bootcamp – Thermal Live™ is switching things up in 2020 and is partnering with Semi-Therm to bring you a new one-day training course event in the Fundamentals of Thermal Management. Produced by Electronics Cooling® magazine, and launched in October 2015 for the first time, Thermal Live Bootcamp features webinars and videos... and there is no cost to attend.

For more information about the event

please visit:

thermal.live

Your partner for thermal solutions

# Alpha's Online Heat Sink Customization Quickly and Easily Create a Custom Heat Sink

| Customization Menu                         | Raference drawing          | mation 4. Submit Request |                         | 4                        |                    | 1.000  | ectly outlomization 2       | Ratelew cuttor<br>Raterence |             | noturnoti intornation     | 4 Submt Request             |                |              | _                       |       |

|--------------------------------------------|----------------------------|--------------------------|-------------------------|--------------------------|--------------------|--------|-----------------------------|-----------------------------|-------------|---------------------------|-----------------------------|----------------|--------------|-------------------------|-------|

|                                            |                            |                          |                         | 0                        | 0                  |        |                             |                             | Ì           |                           |                             |                |              |                         |       |

| Although Addresses                         |                            |                          |                         | 0                        | 0                  | - Ass  |                             | 7                           | 15.00       |                           |                             |                |              |                         | •     |

| Station Judien 600.7mmon<br>finat<br>lote: | Langth C.)<br>45.00        |                          | 12:00 3:00              |                          |                    | Note:  | enJachen Anl.Colona<br>Cont | @⊖                          | uper Oran ( | Langth(L)<br>67.00        | na Octore II to II fotostal | 24.00 6.00     | 0            |                         |       |

| stimated Price<br>Without Tax):            |                            | Add Hole [E              | dit/Delete]             |                          |                    | Estima | ited Price<br>ut Tax):      |                             |             |                           | Change Base S               | ize [Edit/Dele | ete]         |                         |       |

| Quantity Unit price (US\$                  |                            |                          | Location<br>from Center | C-bore<br>Component side | C-bore<br>Fln side |        | ity Unit price (US\$)       |                             | se Width    |                           |                             | Base Length    |              |                         |       |

| 1 122.73<br>5 29.29                        | THF                        | J HII Heliloval Alea     |                         | Diameter Depth           |                    | 1      | 162.35<br>43.56             |                             | 115         | The cut                   | section interferes wit      |                | ested size 6 | 35.3mm or 68            | .8 mm |

| 10 10.01                                   | 1 4.5 Throu                |                          |                         |                          | · ·                | 10     | 28.71                       |                             |             |                           | Add Hole [I                 | Locat          | tion         | C-bore                  | C-bo  |

| 50 5.56<br>100 4.31                        | 2 4.5 Throu<br>3 4.5 Throu |                          |                         | · ·                      |                    | 50     |                             | ID                          | Diameter    | Effective Length/<br>THRU | Fin Removal Area            |                |              | omponent sid            |       |

| 200 RFQ                                    | 4 4.5 Throu                |                          |                         |                          |                    | 200    |                             | 1                           | 6           | Through                   | 8                           | X-axis<br>15   |              | ameter Dept<br>8.00 2.0 |       |

| Complete Imput                             |                            |                          |                         |                          |                    | Compl  | ete Imput                   | 2                           | 6           | Through                   | 8                           |                |              | 8.00 2.0                |       |

|                                            |                            |                          |                         | CI.                      |                    |        |                             |                             |             |                           | Add Tap                     |                |              |                         |       |

|                                            |                            |                          |                         |                          | · · · ·            |        |                             | J                           |             |                           |                             | Í              |              |                         | 1     |

#### Proto lead time 1-2 weeks

Typical production lead time is 2-3 weeks.

### No NRE fee

In most cases, a tooling fee will not be required.

#### No MOQ, No Min. order value

Alpha can supply from a single piece to production volumes.

#### **Quick and Easy**

A custom heat sink can be designed in minutes.

ALPHA Co., Ltd. Head Office www.micforg.co.jp 256-1 Ueda, Numazu City, Japan 410-0316 Tel: +81-55-966-0789 Fax: +81-55-966-9192 Email: alpha@micforg.co.jp

ALPHA NOVATECH, INC. USA Subsidiary www.alphanovatech.com 473 Sapena Ct. #12, Santa Clara, CA 95054 USA Tel: +1-408-567-8082 Fax: +1-408-567-8053 Email: sales@alphanovatech.com

#### www.alphanovatech.com

# CONTENTS

#### **2 EDITORIAL**

Genevieve Martin

#### **4 COOLING EVENTS**

News of Upcoming 2020 Thermal Management Events

#### **6 CALCULATION CORNER**

Application of Transient Thermal Methods to Moisture Diffusion Calculations, Part I Bruce Guenin

#### **12 THERMAL FACTS & FAIRY TALES**

Fairy Tales About Heat Sink Performance Calculations Clemens J.M. Lasance

#### **16 STATISTICS CORNER**

**Probability** Ross Wilcoxon

#### 20 MECHANICAL CYCLING RELIABILITY TESTING OF TIMS DEVELOPED SPECIFICALLY FOR SEMICONDUCTOR TEST

David Saums, Tim Jensen, Carol Gowans, Ron Hunadi, Mohamad Abo Ras

#### 26 THERMAL MANAGEMENT OF CHIP-ON-BOARD LED SYSTEMS AND THEIR AGING RESPONSE TO CYCLIC POWER

Lisa Mitterhuber, Julien Magnien, Elke Kraker

#### 30 SOLDER JOINT LIFETIME OF RAPIDLY CYCLED LED COMPONENTS

Wendy Luiten

#### **35 TECHNICAL EDITORS SPOTLIGHT**

**36 INDEX OF ADVERTISERS**

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, or stored in a retrieval system of any nature, without the prior written permission of the publishers (except in accordance with the Copyright Designs and Patents Act 1988).

The opinions expressed in the articles, letters and other contributions included in this publication are those of the authors and the publication of such articles, letters or other contributions does not necessarily imply that such opinions are those of the publisher. In addition, the publishers cannot accept any responsibility for any legal or other consequences which may arise directly or indirectly as a result of the use or adaptation of any of the material or information in this publication.

ElectronicsCooling is a trademark of Mentor Graphics Corporation and its use is licensed to Lectrix. Lectrix is solely responsible for all content published, linked to, or otherwise presented in conjunction with the ElectronicsCooling trademark.

#### F R E E S U B S C R I P T I O N S

Lectrix®, Electronics Cooling®—The 2020 Spring Edition is distributed annually at no charge to engineers and managers engaged in the application, selection, design, test, specification or procurement of electronic components, systems, materials, equipment, facilities or related fabrication services. Subscriptions are available through electronics-cooling.com.

# **Gelectronics** www.electronics-cooling.com

#### PUBLISHED BY

Lectrix 1000 Germantown Pike, F-2 Plymouth Meeting, PA 19462 USA Phone: +1 484-688-0300; Fax:+1 484-688-0303 info@lectrixgroup.com www.lectrixgroup.com

CHIEF EXECUTIVE OFFICER Graham Kilshaw | Graham@lectrixgroup.com

VP OF MARKETING Geoffrey Forman | Geoff@lectrixgroup.com

EDITORIAL DIRECTOR Jennifer Arroyo | Jennifer@lectrixgroup.com

CREATIVE DIRECTOR Chris Bower | Chris@lectrixgroup.com

BUSINESS DEVELOPMENT DIRECTOR Janet Ward | Jan@lectrixgroup.com

BUSINESS DEVELOPMENT DIRECTOR Mark Pantalone | Mark@lectrixgroup.com

PRODUCTION COORDINATOR Jessica Stewart | Jessica@lectrixgroup.com

LEAD GRAPHIC DESIGNER Kristen Tully | Kristen@lectrixgroup.com

CONTENT MARKETING MANAGER Danielle Cantor | Danielle@lectrixgroup.com

ADMINISTRATIVE MANAGER Eileen Ambler | Eileen@lectrixgroup.com

ACCOUNTING ASSISTANT Susan Kavetski | Susan@lectrixgroup.com

#### EDITORIAL BOARD

Bruce Guenin, Ph.D. Consultant San Diego, CA sdengr-bguenin@usa.net

Ross Wilcoxon, Ph.D. Associate Director Collins Aerospace ross.wilcoxon@collins.cor

Genevieve Martin R&D Manager, Thermal & Mechanics Competence Signify genevieve.martin@signify.com

Victor Chiriac, PhD, ASME Fellow Co-founder and Managing Partner Global Cooling Technology Group vchiriac@gctg-llc.com

SUBSCRIPTIONS ARE FREE Subscribe online at www.electronics-cooling.com

For subscription changes email <u>info@electronic</u>s-cooling.com

Reprints are available on a custom basis at reasonable prices in quantities of 500 or more. Please call +1 484-688-0300.

# LECTRIX

# EDITORIAL

#### **Genevieve Martin**

Contributing Author

An open letter to our community and devoted readers: What is our future perspective on electronics cooling?

It is my privilege to write this editorial for two reasons: first, it's a celebration of our entering this new decade and secondly, it's my first editorial in this prestigious magazine. I am very honored to join the board of technical editors. *Electronics Cooling*<sup>®</sup> has grown in influence within the community over the years, and is recognized as the premium magazine in the field of electronics cooling and thermal management of electronics systems with articles authored by international experts. It is a great pleasure for me to become part of this family.

Let me introduce myself. I have been involved in the field of thermal management and cooling of electronics, primarily at the product system level, for more than two decades. I have been working in different application areas: consumer, professional and non-professional healthcare products, and lighting. Besides my work as thermal expert,

my key work focus has always been on finding faster ways to design product range architectures, and also finding ways to work seamlessly with related fields like e.g. EMC, acoustic noise, optics, and electronics. For the last three years, I have coordinated the European project Delphi4LED, dealing with the very first model creation of an LED digital twin\*. We have successfully managed to integrate, within a single model, a multi-domain (thermal-optical-electrical) digital representation that encompasses the die, package, and product use levels. In addition to my role as an expert in the field, at Signify (formerly Philips Lighting), I lead the thermal management and mechanics worldwide competence and also head a team of technology experts.

In this editorial, I would like to take the opportunity to raise the question of the role of the thermal expert in industry. During my career, I have seen the constant struggle over the role of the thermal management expert confirmed during discussions with other professionals. Thermal management has become a "commodity" in the industry context; oftentimes, thermal design is shifted to the mechanical designers or those with other expertise. Without good in-depth knowledge, the outcome can be disastrous; potential consequences of poor designs can include early failures of products, in terms of reliability or performance. This can result in the involvement of thermal management experts at the end of the design process, where opportunities for design changes are limited or resulting in high cost. Despite years of education of the community at large, this still happens nowadays in industry.

In brief, we all recognize that the thermal management essentially is managing waste, with all other domains considered as primary functions. However, we also know that our field remains important to fulfill performance, safety, reliability, and lifetime of products. There is hope. What new trends are making us stay relevant? With the advent of digital manufacturing, digital industry (production 4.E, Industry 4.0), I believe that our expertise is well equipped to embrace and integrate this new knowledge in early phases of product development. The growing digitalization of our competence over the past decades and our virtual prototyping capabilities give us some advantages compared to other domains. In addition, virtual prototyping without validation is non-viable. Therefore, we need to continue developing more efficient ways of characterization and measurements to feed our models.

From a collaboration perspective, we are well-positioned since our expertise has always required electronics cooling designers to work closely with those providing key functions, forcing us to understand the needs of those in other areas of expertise and translate their needs into the right inputs as well as communicate our results back to them in their "language".

Next, I'll speak to knowledge sharing to advance our community. Communicating new ideas and results at the leading edge of science is an important part of the scientific process and it is my goal to continue with the rest of the *Electronics Cooling*<sup>®</sup> team to bring forward new topics and enable greater visibility of high-quality research at the international level. International scientific sharing is the key to pursue high-level and world-class science research. In this regard, *Electronics Cooling*<sup>®</sup> benefits from all of your scientific contributions and the excellence that the international community has built since more than four decades. All our published articles are carefully reviewed to provide you with the best possible quality of content.

This is also our role and duty to educate and motivate the young researchers, scientists, and engineers to think differently in order to shape the future landscape of our competence field. I therefore invite you to contact us if you have suggestions regarding topics you want to share or read in upcoming issues.

I wish all of you a lot of reading pleasure for the coming year.

#### - Genevieve Martin

\* A virtual counterpart that can mimic the physical attributes and dynamic performance of its physical twin in a simulation environment.

Our high density forged copper heat sink with a mirror grade surface will presit to insure the maximum performance (and life ) of your chip.

> Material crystal structure comparison (100 x) after forged before forged

lower density

higher density

Forging can improved thermal conductivity 5-10% on average

#### ENZOTECHNOLOGY CORP.

Address: 14776 Yorba Ct. Chino, CA 91710 USA Tel : 909-993-5140 Fax : 909-993-5141 E-mail : info@enzotechnology.com Website : www.enzotechnology.com

# COOLING EVENTS

## News of Upcoming 2020 Thermal Management Events

#### EUROSIME

Vienna House Andel's, Cracow, Poland

International Conference on Thermal, Mechanical, and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems.

Desc. source: electronics-cooling.comwww.eurosime.org

**INTERNATIONAL CONFERENCE AND EXHIBITION ON THERMAL & POWER SOLUTIONS** Albuquerque Marriott Pyramid North, San Francisco Rd, NE, USA

NEW THIS YEAR – A TECHNOLOGY CROSS-OVER EXTRAVAGANZA! CICMT, High Temperature, and Thermal & Power Packaging come together for a great opportunity for you...One location | One registration | Three times the content, networking, and learning! The Thermal event has also been upgraded from a Workshop to a full Conference to allow for more attendees, exhibitors, speakers, and networking!

Previously, this event has been organized annually by IMAPS (since 1992 in Workshop format) to specifically address current market needs and corresponding technical developments for electronics thermal management. Presentations on leading-edge developments in thermal management components, materials, and systems solutions for effectively dissipating heat from microelectronic devices and systems are sought from industry and academia. The Workshop emphasizes practical, high-performance solutions that target current and evolving requirements in mobile, computing, telecom, power electronics, military, and aerospace systems. Single-company product development concepts are acceptable subjects; however, all abstracts will be judged on their novelty and innovative contributions to the industry knowledge.

Desc. source: electronics-cooling.com

www.imaps.org/thermal/

#### THERMAL LIVE BOOTCAMP

Online Event

*Electronics Cooling*<sup>®</sup> and Semi-Therm are partnering to bring you a new online training course on the Fundamentals of Thermal Management. Attendees will learn from the experts with a webinar and live Q&A session.

Desc. source: electronics-cooling.com

www.thermal.live

#### **IEEE ITHERM CONFERENCE**

Walt Disney World Swan and Dolphin Hotel, Lake Buena Vista, FL, USA

Sponsored by the IEEE's Electronics Packaging Society (EPS), ITherm 2020 is an international conference for scientific and engineering exploration of thermal, thermomechanical and emerging technology issues associated with electronic devices, packages, and systems. The first ITherm Conference was held in 1988, making this the 31st year of the Conference Series.

Desc. source: electronics-cooling.com www.ieee-itherm.net/itherm/conference/home

#### ADVANCEMENTS IN THERMAL MANAGEMENT

Hilton Denver City Center, Denver, CO, USA

Advancements in Thermal Management educates attendees on the latest advancements in thermal management and temperature mitigation technologies. It is designed for design engineers, academia, system engineers, material scientists, CTOs, and R&D managers with organizations in industries and markets whose products, operations, and services depend upon sophisticated and precise control of thermal properties and states.

Desc. source: electronics-cooling.comwww.thermalconference.com/conference

#### THERMINIC 2020

Fraunhofer Center, Berlin, Germany

26th International Workshop - Thermal Investigations of ICs and Systems.

Desc. source: electronics-cooling.com

www.therminic2020.eu/

#### THERMAL MANAGEMENT SYSTEMS SYMPOSIUM

Sheraton Mesa Hotel, Mesa, AZ, USA

The Thermal Management Systems Symposium, organized by the SAE International will take place from October 6-8, 2020 in Mesa, United States Of America. The conference will cover areas like Mobile air conditioning systems, require new concepts to provide passenger compartment heating and cooling as well as heating and cooling of batteries and cooling of vehicle fuel systems.

Desc. source: electronics-cooling.comwww.10times.com/thermal-management-systems-mesa

#### THERMAL LIVE 2020 Online Event

THERMAL LIVE 2020 is a Free "online" learning and networking event for engineers to learn about the latest topics in thermal management. Produced by *Electronic Cooling*<sup>®</sup>, it showcases the newest techniques and products in the industry.

Desc. source: electronics-cooling.comwww.thermal.live

# Application of Transient Thermal Methods to Moisture Diffusion Calculations, Part I

Reprinted from the *Electronics Cooling®* 2012, Winter Issue

**Bruce Guenin** Assoc. Technical Editor

#### **INTRODUCTION**

Many of the components currently used in electronics systems employ organic materials. Under certain circumstances, the diffusion of moisture into electronic components can lead to problems in the electrical performance and overall reliability of these components. Examples are the increase in the attenuation of high frequency signals in printed circuit boards and package substrates [1], reduction in optical fiber mechanical strength [2], and popcorn failure of organic packages during soldering operations[3].

On occasion, it is necessary to predict the rate of diffusion of moisture in organic materials in order to successfully manage these technical issues. The expertise for performing these calculations is often a rare commodity in engineering organizations. However, analogies between heat flow and moisture diffusion can be leveraged to allow the thermal engineer to perform accurate diffusion calculations by appropriately adapting more familiar thermal methods[4].

This article provides a procedure for quantifying moisture diffusion using a method, developed in a previous column, for the analysis of thermal transient problems involving the numerical solution of a multi-stage resistor-capacitor (RC) circuit [5,6].

#### **MOISTURE DIFFUSION EXAMPLES**

There are many situations in which the diffusion of moisture occurs in organic materials used in electronics hardware. Some are intentional such as: exposure to elevated temperature/humidity in conjunction with reliability or performance testing; and bake out procedures intended to promote the removal of moisture from components to avoid moisture-induced failures. Other exposures may occur in the field, while equipment is being stored in humid environments. Lastly, elevated temperatures resulting from equipment operation will reduce the moisture content of electronic components. In all of these cases it is important to be able to calculate the rate of moisture diffusion, both into and out of the components of interest and to determine the moisture concentration at any time during the exposure.

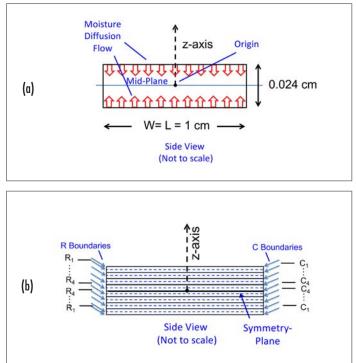

Part 1 of this article deals with a simple one-dimensional moisture diffusion situation at a constant temperature, that can be applied to many situations of interest. Part 2 will deal with a 2D moisture

flow situation encountered in laminate semiconductor packages, both at a uniform temperature and under a thermal gradient resulting from the self-heating of the package.

#### **CALCULATION METHOD**

The basic equations governing heat flow and diffusion presented are indicated below. *Equation 1* is commonly referred to as Fourier's heat equation and *Equation 2* as Fick's first Law of diffusion.

$$\vec{q} = -k\nabla T \tag{1}$$

$$\vec{J} = -D\nabla Conc \tag{2}$$

In each case, the magnitude of a vector field (the flowing entity: thermal energy, q, or the mass flux of the diffusing substance, J, is determined by the product of the gradient of a scalar field (temperature, T, or concentration, Conc) and a rate-limiting parameter (thermal conductivity, k, or diffusion coefficient, D). [Author's note: a common symbol for concentration is C. In this article, the non-standard symbol, Conc, is used to represent concentration, since the symbol C has already been appropriated in this series of articles to mean capacitance.] When calculating either transient heat flow or mass flow using an RC circuit, the resistance is calculated using an appropriate equation containing the thermal conductivity or diffusivity and appropriate terms representing the geometry. The capacitance is equal to the heat capacity in the case of the thermal problem. For the diffusion problem, it is simply the volume of the component or region of interest. These analogies between heat flow and mass diffusion are summarized in Table 1, which also includes those governing electron flow.

|                             | Table 1. Electrical - Ther | mal - Diffusion Analogy  | 1                |

|-----------------------------|----------------------------|--------------------------|------------------|

| Eqn Name                    | Ohm's Law                  | Fourier's Law            | Fick's 1st Law   |

| Entity Flowing              | Elec Charge                | Heat Energy              | Mass of Moisture |

| Potential: to<br>drive flow | Voltage                    | Temperature              | Moisture Conc    |

| Rate-limiting<br>Mat Prop   | Electrical Cond.           | Thermal Cond.            | Diffusion Coef.  |

| C Lumped Element            | Capacitance                | Heat Capacity            | Volume           |

|                             |                            | Function of geometry and |                  |

| R Lumped Element            | Electrical Cond.           | Thermal Cond.            | Diffusion Coef.  |

In a recent installment of this column, a numerical solution of a multi-stage RC circuit was described and applied to the thermal analysis of a high-power chip in thermal contact with a heat sink [5, 6]. This method can be applied directly to the diffusion problem, with appropriately calculated values of R and C.

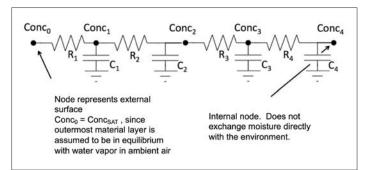

The RC circuit assumed for the current calculations is presented in *Figure 1*. It is a four-stage RC circuit, representing moisture flow from an external surface, represented by node 0, and flowing in a series fashion through four successive regions. The fourth node is an internal one and is not directly connected to the environment. These regions can be parts of a single component or material, or they can be different materials.

Figure 1: Four-stage transient RC circuit representing the diffusion process.

*Figure 2* illustrates the operation of the numerical model, within a given time step, at a single stage in the circuit, in partitioning the incoming mass of moisture,  $M_{IN}$ , into a portion flowing into capacitor  $C_i$  and a portion flowing through  $R_i$  into the adjacent node i+1. A detailed description of the numerical method, along with recipe for implementing it in a spreadsheet are found in Reference [5].

Figure 2: Single stage in RC network illustrating mass transfer in a single time step of the numerical model.

#### **MODEL ASSUMPTIONS**

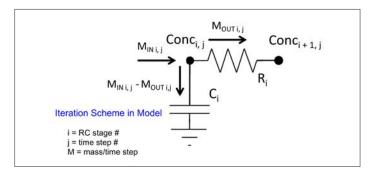

*Figure 3* depicts a common situation encountered in diffusion problems: a slab of homogeneous material in which moisture diffuses from the top and bottom surfaces toward the mid-plane. Diffusion from the edges is neglected, due to their much smaller surface area. The material is assumed to be BT (bismaleimide triazine), a dielectric material commonly used in laminate semiconductor packages.

Two different environmental exposures are assumed: 1) 85°C/85% RH "soak" and 2) 105°C "bakeout." In each case, the process is allowed to continue to completion; i.e.: the soak process achieves the saturation concentration of moisture throughout the sample and the bakeout process drives all moisture from the sample.

The sample thickness is somewhat arbitrary, but is representative of that for a single layer of a package laminate.

Figure 3: (a) Diagram of diffusion sample b) Diagram of boundaries for capacitor regions (solid lines) and resistor regions (dotted lines). Equations shown, for calculating R and C values, representing 1D diffusion.

#### **DIFFUSION PROPERTIES**

Two material properties are needed to perform diffusion calculations: the diffusion coefficient, D, and the saturated concentration of moisture ( $Conc_{SAT}$ ).  $Conc_{SAT}$  represents an upper limit for the moisture content of a particular organic material at given values of T and RH. These properties for the soak conditions were obtained from the literature [7]. To obtain a value for D at 105°C for BT, it was necessary to calculate the activation energy, based on data from this reference taken at 50°C and 85°C, and extrapolate the data to 105°C. The following equation relates the diffusion coefficient to the activation energy, U, where T is the absolute temperature and k equals Boltzmann's constant.

$$D = D_0 \bullet e^{\left(-U_{kT}\right)} \tag{3}$$

Because of the functional form of this equation, log(D) is a linear function of 1/T, with the slope proportional to U.

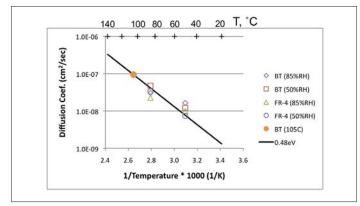

An activation energy equal to 0.48 eV was derived from a best-fit

process. This method has been previously applied to the analysis of diffusion constants for epoxy molding compound [8]. *Figure 4* displays the resulting graph. Given the fact that diffusion coefficient data may not be available at the particular temperature(s) of interest, this method could be very valuable in deriving values of D at the required temperatures. [Note: the reader should be aware of the sensitivity of the resultant value of D to errors in calculating the activation energy when applying this equation, due to its non-linear nature A ±2% error in the activation energy will yield a ±30% error in D.]

Figure 4: Plot of diffusion coefficient values versus 1/Temperature, on log-log scale. Line is fitted through data to predict diffusion coefficient at 105°C.

Reference [7] is also valuable in this regard, since it provides values of  $\text{Conc}_{\text{SAT}}$  for a number of organic materials commonly used in laminate and PCB fabrication over a range of values of T and RH. Reference [9] provides moisture-related data for a wide variety of polymeric materials.

Reference [7] also provides a value for percent of moisture, by weight, equal to 0.5%, for a BT sample after saturation at 85°C/85% RH. This is transformed into  $\text{Conc}_{\text{SAT}}$ , the chosen parameter for this calculation, by multiplying it by the mass density of BT. The  $\text{Conc}_{\text{SAT}}$  for the 105°C condition was set at 0. The rationale for this choice was that the typical bakeout oven is open to the atmosphere. The partial pressure of water vapor at moderate levels of RH in the room containing the oven represents less than 1% RH at 105°C. *Table 2* summarizes the material properties used in the subsequent calculations.

|          |             | Table 2              | . Material Pro | operties |           | ·                 |

|----------|-------------|----------------------|----------------|----------|-----------|-------------------|

| Material | Temperature | Relative<br>Humidity | Density        | H20 Co   | onc. Sat. | Diffusion<br>Coef |

|          | (°C)        | (%)                  | gm/cm3         | (Wt. %)  | mg/cm3    | cm2/sec           |

|          | 20          | N/A                  | 1.77           | N/A      | N/A       | N/A               |

| BT       | 85          | 85                   | N/A            | 0.5%     | 8.85      | 3.03E-08          |

|          | 105         | 0                    | N/A            | 0        | 0         | 9.44E-08          |

#### **CALCULATION OF R AND C VALUES**

When the transient thermal method in References [5] and [6] was applied to a chip + package + heat sink configuration, the physical model was composed of distinct components made of differing materials. Consequently the partitioning of the physical model into discrete R and C regions was rather straightforward. The present example differs from this earlier one since it consists of a single material.

The method used in the current problem is as follows.

- Since there is a symmetry plane at z = 0, it is only necessary to solve for one half of the model. Due to symmetry, this solution applies to both halves.

- Divide each half-model into four separate cuboidal C regions of equal volume. The thickness of of each cuboid is equal to 1/8 times the total sample thickness =  $1/8 \ge 0.024 = 0.003$  cm.

- The R regions are assumed to connect the centroid plane of each C region to that of its neighbor. Hence, the  $\Delta z$  value associated with each of these resistances would be 0.003 cm. The one exception is for the resistance between outermost C region (C1) and the exterior surface. In this case, the  $\Delta z$  value (for R1) would be 0.0015 cm.

The spatial boundaries of the different R and C regions are illustrated in *Figure 3b*. The figure also indicates the formulas for calculating the R and C values for a 1-D diffusion situation. *Table 3* provides the dimensions of each region and the calculated values of R and C based on the appropriate value of D and the specified geometry.

|                |        | Table | 3. Calculated V | alues of R a         | nd C     |          |       |

|----------------|--------|-------|-----------------|----------------------|----------|----------|-------|

| Lumped         | Δz     | Area  | Temperature     | Relative<br>Humidity | D        | R        | C     |

| Element        | (cm)   | (cm2) | (°C)            | (%)                  | cm2/sec  | sec/cm3  | cm3   |

| R1             | 0.0015 | 1     | 0.5             | 07                   | 3.03E-08 | 4.95E+04 |       |

| R2, R3, R4     | 0.003  | 1     | 85              | 85                   | 3.03E-08 | 9.90E+04 | N /A  |

| R1             | 0.0015 | 1     | 107             | 0                    | 9.44E-08 | 1.59E+04 | N/A   |

| R2, R3, R4     | 0.003  | 1     | 105             | 0                    | 9.44E-08 | 3.18E+04 |       |

| C1, C2, C3, C4 | 0.003  | 1     | N/A             | N/A                  | N/A      | N/A      | 0.003 |

#### **DIFFUSION SIMULATION RESULTS**

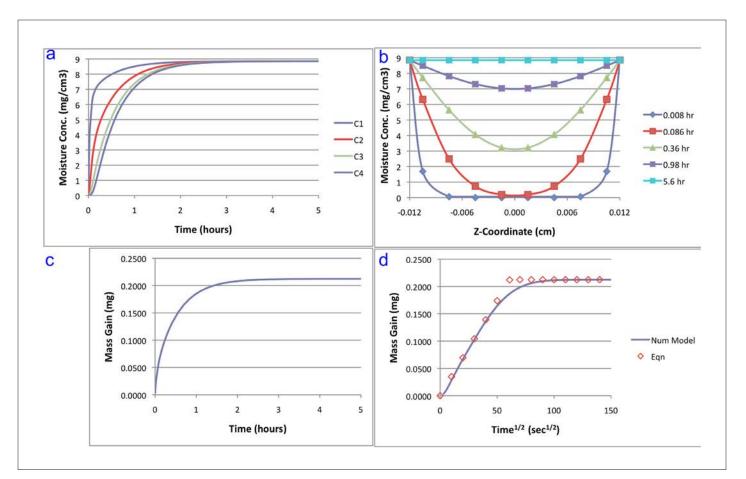

*Figure 5* displays four graphs illustrating various aspects of the transient moisture behavior of the sample as it is transferred from a dry environment into the 85°C/85% RH soak environment. *Figure 5a* plots the value of the moisture concentration in each of the four C regions. Region C1, representing the outermost region, responds most quickly. Conversely, region C4, associated with the innermost region, adjoining the symmetry plane, is the slowest to respond. *Figure 5b* plots each value of moisture concentration of the centroid of each C region. Results for all regions of the sample, both above and below the symmetry plane are plotted to assist visualization of the 2D moisture concentration profile. It illustrates the time lag involved with the center region of the sample ultimately achieving moisture equilibrium with its environment.

*Figure 5c* plots the total mass of absorbed moisture versus time. It is calculated using the following equation. The prefactor of two results from the half-symmetry of the model.

Figure 5: Solution results for BT sample, 85° C/85% RH soak exposure. a) Concentration values at each capacitor. b) 2-D diffusion profile versus time. c) Mass gain curve, linear time scale. d) Mass gain curve versus time 1/2.

$$M_{H_2O} = 2 \bullet \sum_{i=1}^{4} Conc_i \bullet C_i \tag{4}$$

The shape of the  $M_{H20}$  vs time curve is that expected in a soak situation. Its time constant (time to reach 63% of the saturated value) is 0.42 hours.

Finally, *Figure 5d* plots the total mass of absorbed moisture versus time<sup>1/2</sup>. This is a useful way of plotting diffusion data since the slope of the  $M_{H2O}$  vs time<sup>1/2</sup> is a constant in the initial part of the diffusion transient. This behavior is quantified in *Equation 5*,

$$M_{H_{2O}} = k \bullet t^{1/2}, where \ k = \frac{4M_{SAT}}{l} \left(\frac{\pi}{D}\right)^{1/2}$$

(5)

where l is the thickness of the sample, which is assumed to be exposed to moisture from two opposing sides [6].

The symbols in *Figure 5d* for values  $< M_{SAT}$  are generated using the above equation. This serves as a validation of the numerical procedure. Also, it serves as an analytical method for approximating the  $M_{H20}$  vs time curve it simple situations such as this, not requiring the precision of the numerical model.

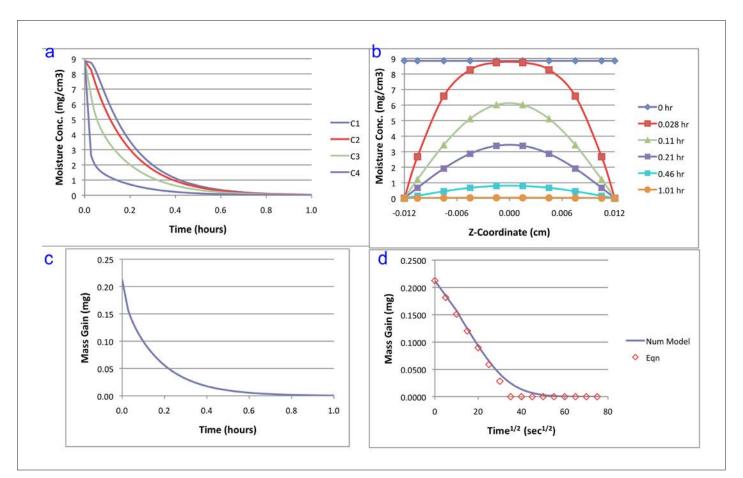

The corresponding curves for the bake environment are shown in *Figure 6*. The sample is assumed to have been fully saturated with moisture from the 85°C/85% RH at the moment it is placed into the bakeout oven at 125°C. Qualitatively, the moisture versus time curves are the inverse of those in *Figure 5*. Quantitatively, however, the time constant for the bake process is approximately one-third of that in the soak process and is equal to 0.14 hour. This is due to the fact that at 125°C, D is approximately three times its value at 85°C. *Figure 6b* indicates, as before, that the moisture concentration at the center of the sample lags considerably behind the outer regions in equilibrating with the new, dry environment. The predicted curve in *Figure 6d* shows good agreement with the symbols, whose  $M_{\rm H20}$  values were calculated using *Equation 4* at the higher value of D, and where the slope was assigned a negative sign.

#### COMMENTS REGARDING THE GENERALITY OF THIS METHOD

The method presented here has been applied to a situation that could have been handled readily using purely analytical methods [2, 7, and 8]. The rationale for doing so was to use a simple example for demonstrating the method clearly and to be able to use the accompanying analytical solution to validate the numerical model.

Figure 6: Solution results for BT sample, 105°C/0% RH bake exposure. a) Concentration values at each capacitor. b) 2-D diffusion profile versus time. c) Mass gain curve, linear time scale. d) Mass gain curve versus time1/2.

The RC circuit demonstrated herein can be adapted to a greater range of geometries, since elements representing different geometrical "primitives" can be combined [10]. Furthermore, it is possible to modify the numerical solution to accommodate parallel flux paths, to provide even more adaptability to a variety of applications [11]. Alternatively, it is possible to use SPICE-type electrical circuit simulation software to perform these calculations [12]. In contrast, closed-form analytical methods are generally limited to simple geometries, typically cuboids, cylinders, and spheres.

#### REFERENCES

- J. Miller, Y. Li, K. Hinckley, G. Blando, B. Guenin, and I. Novak," Temperature and Moisture Dependence of PCB and Package Traces and the Impact on Signal Performance," Proceedings DesignCon Conference, Santa Clara, January 30 – February 2, 2012

- J. Mrotek, J. Matthewson, and C. Kurkjian, "Diffusion of Moisture Through Optical Fiber Coatings," J. Lightwave Tech., Vol 19, No. 7, (2001), pp. 988-993.

- A. Xiao, G. Schlottig, H. Pape, B. Wunderle, K M. B. Jansen, L. J. Ernst, "Delamination and Combined Compound Cracking of EMC-Copper Interfaces," Proceedings ECTC Conference (2010) pp. 114–120.

- 4. J. Wilson, "Moisture Permeation in Electronics," ElectronicsCooling, Vol. 13, No. 2 (2007).

- 5. B. Guenin, "Transient Modeling of a High-Power IC Package, Part1," ElectronicsCooling, Vol. 17, No. 4 (2011).

- 6. B. Guenin, "Transient Modeling of a High-Power IC Package, Part2," ElectronicsCooling, Vol. 18, No. 1 (2012).

- M. Pecht, H. Ardebili, A. Shukla, J. Hagge, and D. Jennings, "Moisture Ingress Into Organic Laminates," IEEE Trans. Comp. Pack. Tech., Vol. 22, No. 1, (1999) pp. 104-110.

- 8. A. Teverovsky, "Characteristic Times of Moisture Diffusion and Bake-out Conditions for Plastic Encapsulated Parts," NASA white paper, October 15, 2002, available for download at https://nepp.nasa.gov.

- L. K. Massey "Permeability Properties of Plastics and Elastomers: A Guide to Packaging and Barrier Materials,2nd Ed." Plastics Design Library.

- B. Guenin, "Heat Spreading Calculations Using Thermal Circuit Elements," ElectronicsCooling, Vol. 16, No. 3, August, 2010.

- B. Guenin, "Transient Thermal Model for the MQUAD Microelectronic Package," Proceedings SEMI-THERM X Conference, February, 1994, pp. 86-95.

- 12. See, for example: http://en.wikipedia.org/wiki/SPICE.

Transient Simulation (Warm-up case)

20 15 10

# Simcenter Flotherm<sup>™</sup> XT

**Discover a CAD-centric thermal** simulation approach

Camera Module - 01

um

- Compress the electronics cooling design process by bridging EDA & MCAD design flows

- Accurately model complex shaped geometry with robust automated meshing

www.mentor.com/mechanical

## THERMAL FACTS & FAIRY TALES

# Fairy Tales About Heat Sink Performance Calculations

Reprinted from the Electronics Cooling® 2016, September Issue

#### Clemens J.M. Lasance,

Guest Editor, Philips Research Emeritus, Consultant@SomelikeitCool

#### **INTRODUCTION**

When Peter Rodgers invited me to again write a Thermal Facts and Fairy Tales (TF&F) column, I immediately thought of a recent webinar on basic heat sink calculations that I attended, in order to get an idea of the current status-quo in these matters. Well, in my humble view there was room for improvement. Apart from certain minor issues, I was triggered by three topics that I felt were not treated in a correct way when dealing with practical situations, namely;

- The fact that a heat sink does not only function as an area enlarger

- A much-too-simple explanation of the apparent (effective) emissivity of heat sinks

- The (mis)use of heat sink convective heat transfer correlations

With these three topics in mind, this TF&F column aims to outline my two cents on these issues.

#### A HEAT SINK HAS TWO FUNCTIONS

This topic has been treated *in extenso* in references [1, 2], with a summary provided here. One should realize that a heat sink performs two very different functions:

- Enlarge the surface area for heat transfer

- Spread the heat (providing a significant temperature gradient exists over the dissipating surface)

Suppose we wish to calculate the effect of a heat sink attached to an arbitrary generic electronic component without modelling all component-heat sink details. The first function is easy to address: simply multiply the real-life convective heat transfer coefficient by the area enlargement factor to obtain an effective heat transfer coefficient. It is the second function that can cause a problem when we need to consider the temperature gradient over the component surface that the heat sink is to be attached to. For this analysis, let's start by dividing the component surface into two areas: the central and periphery. When the heat sink is attached, the heat spreading reduces the maximum temperature of the central area and increases the minimum temperature in the peripheral region. This means that the effective heat transfer coefficient of the central area (required to lower its temperature is through addition of the heat sink base only) is significantly increased. Reference [1] highlights this aspect when a considerable increase in the average central heat transfer coefficient results, compared to the overall average value, i.e. 100 W/m<sup>2</sup>K versus 8 W/m<sup>2</sup>K, for a natural convection application. In this context, if we want to generate a heat sink compact model to increase the efficiency of computational auid dynamic (CFD) models, it is therefore mandatory to always explicitly model the heat sink base, with a compact description added for the remaining fin structure. Here is a first order estimation of this effect: suppose that for certain components that exhibit a significant surface temperature gradient, the central area is one quarter of the total area, and its effective heat transfer coefficient is 12 times higher than on the peripheral area, then the influence of the base is about as strong as a threefold total area extension.

## THE QUESTION ABOUT THE APPARENT EMISSIVITY OF HEAT SINKS

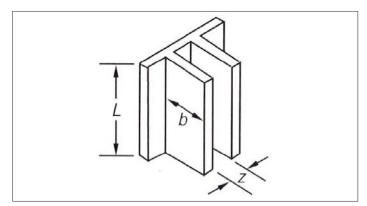

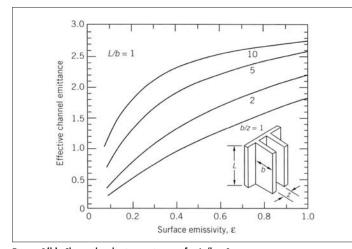

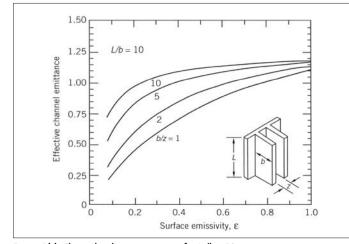

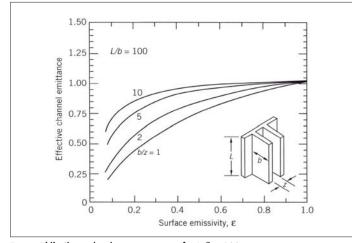

The analytical calculation of the apparent (or effective) emissivity (or emittance) of a heat sink can represent a significant effort as it depends strongly on the heat sink geometry. The apparent heat sink emissivity can be determined with high accuracy by employing radiation network theory, as discussed in pages 291-303 of reference [3]. However such calculations are no longer necessary in the age of computer-aided engineering software having embedded radiation calculation options. Let us define the heat sink geometry as shown in *Figure 1(a)*.

Figure 1(a): Heat Sink Geometry

Figure 1(b): Channel radiative emittance for L/b = 1.

Figure 1(c): Channel radiative emittance for L/b = 10.

Figure 1(d): Channel radiative emittance for L/b = 100.

*Figure 1.* Effective (apparent) channel emittance (emissivity) for various heat sink geometries (taken from [3]).

The subsequent graphs shown in *Figures 1b* to *1d* provide a realistic impression of what to expect. Herein the apparent emissivity

is related to the base surface area without fins. For short and wide fins (e.g. L/b=1, b/z=1), it is obvious that a considerable part of the additional area is exposed to the environment, and hence its emissivity does matter. Furthermore, because of the extended surface area, the apparent emissivity can be greater than one because the base area is the reference. The opposite is true for long and closely-spaced fins (e.g. L/b=100, b/z=10); in this case its emissivity does not play any role, and the extended area from a radiation point of view is negligible. The point is that the radiation entering the fin channel cannot escape without multiple reflections between the fin channel surfaces. In addition, heat sinks with such a layout are only used for forced convection, hence the radiation contribution to the total heat transfer is minimal anyway. The conclusion must be: don't bother with emissivity calculation for forced convection applications, but do for natural convection, especially for those applications where often widely spaced fins in a non-traditional shape are used, such as in the field of light emitting diode (LED) applications.

In summary, don't trust simple rules of thumb for natural convection applications. Caveat: check upfront if your application is really naturally convection driven. In most cases you will conclude that we encounter buoyancy-induced forced convection [4]. When a heat sink has already been selected, a simple test is recommended: measure the operating temperature drop before and after painting the heat sink.

#### THE (MIS)USE OF HEAT SINK CORRELATIONS

The problems with convective heat transfer correlations for practical purposes are extensively discussed in references [5-7]. Let me quote (a bit adapted) from my TF&F column of June 2015 [7].

The background in a nutshell is that the handbooks showing impressive heat transfer correlations are inherently based upon a set of conditions/constraints that are not satisfied in real life. When you believe in the following axioms, then the "Holy Books of Heat Transfer" are consistent and comprise a wealth of information, very useful for a basic understanding of the physics.

Here are the underlying axioms:

- Uniform boundary conditions, either constant temperature or flux

- Uniform approach aow with a degree of turbulence as close as possible to zero (that's why research type wind tunnels are huge).

- (Very) simple geometries: smooth, fat and thin plates, parallel plate channels, pipes

- Single source, especially for natural convection

- Constant properties

- Fan dynamics based on air flow chamber testing

- Extended surfaces based on Murray-Gardner assumptions (see e.g. [8])

- "Complex shapes" means there exists an analytical solution

- Heat spreading limited to one-layer, one-sided heat transfer

- Radiation diffuse and grey

This means that if and only if the physical situation conforms to the assumptions does the experimenter have the right to assume that the predicted results will be obtained. That means much more than simply matching Nusselt (Nu) with Rayleigh (Ra) or Reynolds (Re) numbers.

Specifically, most analytical (and numerical) studies assume uniform flow velocity with a specified turbulence (often zero), uniform temperature and the origins of the velocity boundary layer and the thermal boundary layer on the surface.

For many fields of heat transfer, such as turbulence, boiling, heat exchangers, channel flow, etc., these axioms form a sound base. **Not so for electronics cooling at the system level.**

Especially when referring to heat sinks, the author published a TF&F column titled "How useful are heat sink correlations" in [9]. Bottom line is that to use correlations to obtain a reasonable estimation of heat sink performance is a fairy tale.

What's wrong is that most equations are based on the following assumptions, in addition to the ones previously listed:

- Parallel plate heat sinks

- Fully ducted flow

- · Fully developed flow

- Strong impact of 3D flow (especially in natural convection) not considered

- Equal number of fins and channels

- Negligible entrance and exit effects

- Laminar and uniform approach flow

- No temperature gradient in heat sink base

- Heat spreading effect of base not taken into account

- Uniform fin temperature (both between fins and within a fin)

Now, have a look at some state-of-the-art heat sink geometries for LED applications in *Figure 2*, in addition to the ones pictured in the December 2013 TF&F column [9].

Is there anyone out there who can tell me with a straight face that a Nusselt number correlation based on parallel-plate heat sinks will predict a realistic performance of these products? I don't think so.

Obviously, if you use handbook equations to base your heat sink design upon, or to predict the performance of a selected heat sink type, chances are high that you may miss all of the heat sinks shown in *Figure 2*. Sure, extrusion-based parallel-plate heat sinks are the cheapest around, but they score badly when it comes to optimization of shape, weight, volume, and performance, especially regarding optimal fin thickness. And the final argument in favor of using CFD codes instead of correlations: 3D printing is a booming business, and for sure parallel plates are not the ones that will be high on the list for optimization.

Figure 2: Non-parallel plate heat sink geometries for LED applications.

#### CONCLUSION

The starting point for this column was my experience with a heat sink webinar. I was not happy with the approach that it was presented, and the reasons why have been outlined in this column.

To all who want to transfer basic heat sink knowledge: tell facts, not fairytales. The fact is that reality is complex. Basic heat transfer about conduction, convection and radiation: OK, but tell the attendees also that in order to realize a competitive edge in eventual sales, much more knowledge is needed than some limited and outdated design rules. Compare it with electronic design: nobody believes that one is capable of designing a functional printed circuit board (PCB) after attending a webinar of half an hour. After this column one should understand why it is not simple to assess heat sink performance, which should be the bottom line.

#### REFERENCES

- Lasance, C.J.M., "The Inauence of Various Common Assumptions on the Boundary-Condition-Independence of Compact Thermal Models," IEEE Transactions on Components and Packaging Technologies, Vol. 27, Issue 3, pp. 523 – 529 (2004).

- [2] Lasance, C.J.M., "Heat Sink Basics from an Industrial Point of View," Chapter 9 in: Thermal Management of LED Applications: Volume 2 – Solid State Lighting Technology and Application, Lasance C.J.M. and Poppe A. (Eds), Springer, New York, USA, pp. 347-387 (2014).

- [3] Kraus, A. and Bar-Cohen, A., Design and Analysis of Heat Sinks, Second Edition, John Wiley and Sons, New York, USA, pp. 291-303 (1997).

- [4] Moffat, R.J. and Ortega, A., "Buoyancy Induced Forced Convection," Heat Transfer in Electronic Equipment, ASME, New York, US, HTD-Vol. 57, pp. 135-144 (1986).

- [5] Lasance, C.J.M., "Sense and Nonsense of Heat Transfer Correlations Applied to Electronics Cooling," in Proceedings of the Sixth Conference on Thermal, Mechanical and Multiphysics Simulation and Experiments in Micro-Electronics and Micro-Systems (EuroSimE), Berlin, Germany, April 18-20, pp 8-16 (2005).

- [6] Lasance, C.J.M., "Most of Us Live neither in Wind Tunnels nor in the World of Nusselt," ElectronicsCooling, June 2010, https://electronics-cooling.com/2010/04/thermal-facts-andfairytales- most-of-us-live-neither-in-wind-tunnels-nor-inthe-world-of-nusselt/, accessed August 5, 2016.

- [7] Lasance, C.J.M, "The Holy Books of Heat Transfer: Facts or Fairy Tales?" ElectronicsCooling, June 2015, https:// electronics-cooling.com/2015/05/the-holy-books-of-heattransfer-facts-orfairytales/, accessed August 5, 2016.

- [8] Kraus, A., Aziz, A., and Welty, J., Extended Surface Heat Transfer, A Willey-Interscience Publication, John Wiley and Sons, New York, USA (2001).

- [9] Lasance, C.J.M., "How Useful are Heat Sink Correlations for Design Purposes?" ElectronicsCooling, December 2013, https://electronics-cooling.com/2013/12/heat-sinkcorrelations-design/, accessed August 5, 2016.

## STATISTICS CORNER

## **Probability**

**Ross Wilcoxon** Assoc. Technical Editor

#### INTRODUCTION

ive decided to introduce a new column to Electronics Cooling Magazine—and it's not just because I have run out of good ideas for "Thermal Facts and Fairy Tales" columns. For 2020, I will publish a series of columns in which I try to provide the readers with some insight into the field of statistics and a few tools for effective use of statistical methods. After a couple of decades in industry, I have observed that a number of experienced engineers can be intimidated by the topic of statistics—these columns will attempt to reduce the level of intimidation. While I have been interested in statistics for a few decades now, I don't claim to be an expert. I will do my best to get things as right as I can, as well as to make things useful and practical.

Statistical analysis is needed because data will always have some degree of uncertainty; a value that we determine from a single measurement, or even set of measurements, is not necessarily going to tell us exactly what value we will determine with additional measurements. Statistical analysis uses the mathematics of probability to create tools that we can use to deal with that uncertainty. This column discusses some aspects of probability concepts to set the basis for how the mathematics of probability can be applied to address uncertainty in statistical analysis.

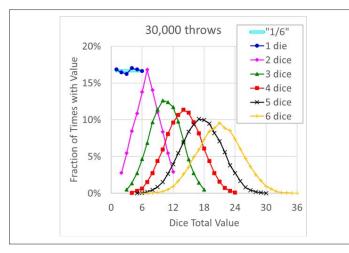

Any discussion of statistical analysis must include a discussion on probability. Since the entire field of probability and statistical analysis began with gamblers attempting to improve their chances of winning, it seems appropriate that this discussion on probability begins with a game of chance: namely, throwing dice.

To begin, I assume that we have an infinite amount of time and patience that allows us to make a lot of throws, the dice that are not loaded (on any given throw they are equally likely to fall with any of its sides up), and we are not playing *Dungeons & Dragons*, so our dice only have six sides. In other words, I will use an Excel spread-sheet to simulate throwing dice. I trust that the random function is, in fact, fairly random, and that I can calculate the result of throwing a die with the equation "=ROUNDDOWN(RAND()\*6,0)+1".

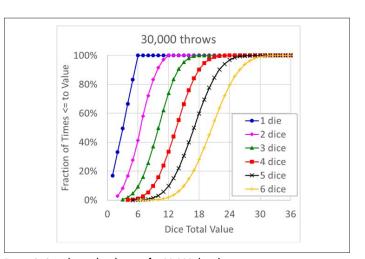

*Figure 1* shows what fraction of 30,000 throws of 1-6 dice, as calculated using a simple Excel spreadsheet, had a total value of one to 36. For a single die, we would expect that the values one through six would each occur approximately 1/6th of the time—which is about what reasonably close to what was found in the calculations. As the number of dice included in the throws increases from one to six, the distributions change from a flat line to a triangle to an increasingly 'bell shaped curve'.

*Figure 2* shows the same data, but plots the cumulative distributions that show what portion of the throws had a total value that was equal to or less than a value between one and 36. One of the

Figure 1: Probability distributions for 30,000 simulated dice throws.

Figure 2: Cumulative distributions for 30,000 dice throws.

fundamental tenets of probability theory is that the probability of the sum of all possible outcomes is equal to one, which is both logical and illustrated in the figure. In these cumulative distributions, the plots transition from a straight line to a 'tilted S shaped curve' as the number of dice increases from one to six.

Readers with some (any?) background in statistics likely can see where this is going—the 'bell' and 'tilted S' shaped curves start to look like the normal distribution that is widely used in statistical analysis. The discussion on that topic will be in the next column in this series.

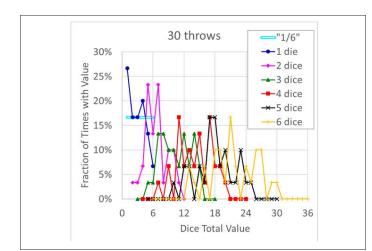

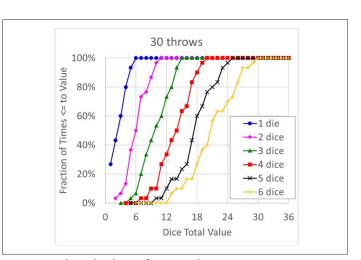

A question that may be asked is "What would happen if we had to use actual dice and we didn't have the time needed to throw them 30,000 times?" Again, we can simulate that, with results shown for the probability and cumulative distributions for sets of only 30 throws of one through six dice in *Figure 3* and *Figure 4*. *Figure 3* is best described as an incoherent mess: for the 'one die' data, two values fell exactly on their expected theoretical value of 16.7%, while two other values were ~60% higher or lower than that. Data for more than one die do not appear to be much better behaved.

While the cumulative data for 30 throws, *Figure 4*, shows considerably more jitter than their counterparts for 30,000 throws (*Figure 2*), the cumulative distributions appear to be much less random than the raw distribution data (*Figure 3*). A comparison of *Figure 3* and the curves that show the same data in *Figure 4* illustrates why some data, such as from reliability testing, is often plotted in terms of a cumulative distribution rather than probability.

If a situation is governed by known physics, it can be relatively straightforward to estimate probabilities of a single event. In the case of rolling a single, non-loaded, six-sided die, it should seem obvious that there is a 1/6th chance of any of the six possible outcomes occurring. However, probability calculations can start to become less intuitive when we begin to consider combinations of multiple events. For example, consider the classic question that is considered to have been the beginning of mathematical analysis of probability—the likelihood of rolling a specific value within a specific number of attempts [1]. De Mere, a gambler in the 1600s, tended to win more often than not when he bet that he would roll a six within four attempts. His reasoning for why he would win was that the chances of rolling a six in one roll was 1/6th, so in four rolls his chances should be 4 \* 1/6 = 2/3. Since that value is larger than 50% and he was playing even odds (the loser pays the same amount regardless of who it is), he had concluded that it was, on average a winning bet. But when he extended the game to two dice and gave himself 24 attempts to roll a double six, which by his reasoning should have had the same probability (24 \* 1/6 \* 1/6 = 2/3), he began to lose money. He asked the mathematician Blaise Pascal to help him understand why his luck had changed.

When calculating probabilities of multiple events, two things that should be kept in mind are that the calculated probability of any outcome must never exceed 100%, and that it is often useful to think in terms of an event not happening. In de Mere's case, one simply has to consider the first point to recognize that his equation was incorrect. If the chances of rolling a six in four attempts is 2/3, then that equation states that the probability of rolling a six in eight attempts will be 133% (4/3). Clearly, this is not possible. To correctly determine the probability of rolling a six in four attempts, one can consider the probability of not rolling a six in one attempt and multiply that times itself four times. The probability of not rolling a six is (5/6 = 83.3%), so the probability of not rolling a six in four attempts is  $(5/6)^4 = 48.2\%$ . Since the probability of not rolling a six in those four attempts plus the probability of rolling a six in the same attempts must equal 100%, the probability of rolling a six in four attempts is 100%-48.2% = 51.8%. This probability is greater than 50%, so with even odds it makes sense that de Mere was coming out ahead. On the other hand, when using the same approach the probability of rolling double sixes in 24 attempts can be calculated as  $1 - (35/36)^{24} = 49.1\%$ , which is less than 50% and therefore not a good bet at even odds.

Figure 3: Probability distributions for 30 Simulated dice throws.

Figure 4: Cumulative distributions for 30 Dice throws.

#### **SUMMARY**

Probability theory is fascinating and, even the most cursory overview of it, encompasses far more than can be addressed in this short article. This is particularly true if one considers the topic of conditional probability [2], in which the probability of an event depends on another probabilistic event. The example described in this article illustrates that, in a reasonably well-behaved population of data, the effects of measurement variability tend to wash out and lead us to familiar-looking distributions. But it may require a lot of samples from that population to get there. If we only look at a small portion of the population, the distribution won't necessarily appear as a nice bell shape.

Future articles in this series will discuss some of the statistical approaches used to extract useful information and understand

the distribution characteristics of data sets that are smaller than 30,000 that led to the smooth curves shown in *Figures 1* and 2. Topics will include different parameters used to characterize a data set, what confidence we have regarding the uncertainty of those parameters, different models for distributions and how to use them, how to determine if one set of data is different from another, how many samples do we need for a given test, etc.

#### **REFERENCES**

- https://introductorystats.wordpress.com/2010/11/12/onegambling-problem-that-launched-modern-probabilitytheory/, accessed August 24, 2019

- https://www.probabilitycourse.com/chapter1/1\_4\_0\_ conditional\_probability.php

#### From the Creators of Electronics Cooling

#### INTRODUCING

#

# THERE'S ONLY ONE SPOTLIGHT ARE YOU INIT?

Positioning Ambitious B2B Electronics Companies for Aggressive Growth

# www.lectrixgroup.com

PHILADELPHIA, PA | HONG KONG

# Mechanical Cycling Reliability Testing of TIMs Developed Specifically for Semiconductor Test

David Saums\*1, Tim Jensen2, Carol Gowans2, Ron Hunadi2, Mohamad Abo Ras3

<sup>1</sup>DS&A LLC, Collaborative Innovation Works, 11 Chestnut Street, Amesbury MA, 01913 USA <sup>2</sup>Indium Corporation, 34 Robinson Road, Clinton NY, 13323 USA <sup>3</sup>Berliner Nanotest und Design GmbH, Volmerstrasse 9B, D-12489 Berlin, Germany

\* Corresponding Author: dsaums@dsa-thermal.com

#### **David Saums**

Dave Saums holds B.S. and MBA degrees from Clarkson University, with post-graduate work at Union College, all in New York. He has 41 years of work experience in electronics thermal management, working for several manufacturers of thermal materials, composites, and thermal management components and systems. He resigned as Vice President of Marketing for a specialty composites manufacturer to found DS&A LLC, a consulting firm focused on technical marketing, business strategy, and new product and business development. A presentation

in 2008, in France, was the first implementation of a pumped two-phase dielectric liquid cooling system to IGBT modules and a complete electrical drive system. He has chaired a thermal management workshop in California as a volunteer for 19 years.

#### Tim Jensen

Tim Jensen is the Senior Product Manager for Indium Corporation's engineered solder materials, the company's most diverse product group, which includes solder preforms, wire, ribbon, and thermal interface materials. He is responsible for ensuring the product line is poised for long-term success by developing technologies that best meet the current and future needs of customers. Tim is a member of the SMTA's Board of Directors, has a bachelor's degree in chemical engineering from Clarkson University and an MBA from Syracuse University, and has

authored numerous technical papers on soldering and thermal technology.

#### Carol Gowans

Carol Gowans has more than 30 years of experience in sales and product management. As the product manager for Indium Corporation's low-temperature products, her current focus is indium and bismuth products, which encompasses a variety of markets including medical, aerospace, cryogenic, and electronics manufacturing. Carol graduated from Utica College with a bachelor's degree in public relations and has authored papers on solder fortification® and improving solder joint reliability with the use of solder preforms.

#### Ron Hunadi

Ron Hunadi has more than 30 years of experience in sales, marketing, and business development in materials for electronics and microelectronics assembly. At Indium Corporation, he is a member of the Global Accounts Team and is responsible for developing new thermal interface business opportunities with large multi-national semiconductor companies. Ron has a bachelor's degree in chemistry from Penn State University, a master's degree and Ph.D. in organic chemistry from the University of California Riverside, and has authored more than 30 articles,

papers, and patents.

#### **Mohamad Abo Ras**

Mohamad Abo Ras received his diploma and Master's degree in Applied Physics and Medical Engineering. During and after his studies, he joined Fraunhofer IZM in Berlin, in the thermal management group and in 2008, Berliner Nanotest und Design GmbH. Main focuses of his research work are development and application of test equipment for material characterization, as well as non-destructive methods for failure analysis. Since 2017, Abo Ras is chief executive officer of Berliner Nanotest und Design GmbH, in Berlin.

#### **KEYWORDS**

*Thermal Resistance | Thermal Interface | Semiconductor Test | Durability | Cycling | Device Under Test*

#### NOMENCLATURE

| DUT  | Device Under Test              |

|------|--------------------------------|

| OSAT | Out-Sourced Assembly and Test  |

| Rth  | Thermal Resistance             |

| S/TB | Semiconductor Test and Burn-In |

| TIM  | Thermal Interface Material     |

|      |                                |

#### ABSTRACT

any thousands of thermal interface materials (TIMs) exist due to the very wide disparity in requirements across an extremely diverse range of market applications throughout the electronics industry. For certain market segments, such as geothermal and downhole petroleum exploration and semiconductor test and burn-in, application requirements may be so significantly challenging as to require development of materials for very specific and unusual requirements, beyond normal computing equipment and power electronic systems requirements. A test program in four phases has been designed to test such newly-developed materials against those very narrowly-defined and unusual requirements. The value of discussing such materials intended for a relatively narrow market segment is that this type of testing and development work can be useful in evaluating how to develop unusual test programs for other material applications. Three newly-developed TIMs designed specifically to address semiconductor test and burn-in (S/TB) requirements were tested and successfully passed each test phase.

#### SEMICONDUCTOR TEST REQUIREMENTS

The semiconductor test industry consists of manufacturers of very specialized test systems, companies that develop relatively complex test heads and sockets configured for specialized IC and power semiconductor packages, and the OSATs and semiconductor manufacturers that must perform testing of every device or according to a sampling regimen. This array of different customers for the TIMs utilized all have differing requirements that must be addressed. A short survey of a limited number of these manufacturers was conducted to develop a test regimen for clamping force, contact duration (dwell), temperature, and what is termed a "strike angle" for a non-parallel contact. Test procedures also include operation over a range of temperatures (typically 115-125°C) for defined periods, and, in certain burn-in tests, temperatures to 155°C. Mechanical test characteristics combined together (zero residue on the DUT, non-parallel contacting surfaces and potential for a strike angle as described, elevated temperatures, thousands of contacts with a single TIM) and this set of requirements is a major challenge for durability for any type of TIM selected.

Semiconductor test parameters include a variety of electrical performance tests for device performance and binning by frequency and other characteristics. Elevated temperatures during burn-in testing are intended to stress and cull early failures. The development of a single TIM type that can withstand many hundreds and thousands of contact cycles is critically important to test throughput and cost of semiconductor test. Some highly specialized devices may be very low unit volume, with only hundreds tested per day, while high-volume manufacturers of microprocessors and ASICs may require testing at rates up to tens of thousands per day. Stopping test programs in order to remove the TIM, clean the test head, and apply a replacement TIM can therefore be exceptionally costly in labor time and in yield.

Many different test head designs exist, to meet differing system requirements. Test is divided into two principal design categories: the use of a monolithic test head (i.e., a unitary flat contact surface facing the DUT), and the use of multiple electrical contact pin probes in an array (where no TIM is used). This discussion deals with the majority design category, the monolithic test head. These test head designs incorporate heating and cooling capabilities within the test head, with complex systems utilizing a liquid cold plate, one or more thermoelectric modules, and heaters, to apply the desired temperature cycles. The TIM must be applied to the flat test head surface facing the DUT.

#### MATERIALS DEVELOPMENT FOR SEMICONDUCTOR TEST

The critical requirement for semiconductor test, regardless of material type, is that any TIM used in contact with a device under test (DUT) must be of a type that does not leave any residue, oil, or contaminant on the surface of the device package (or die surface, if a bare die package). This requirement cannot be waived and eliminates all materials that are polymeric, in pad form, and capable of marking or leaving any detritus (especially electrically conductive), and all compounds such as greases and gels. While semiconductor test and burn-in (S/TB) may be a relatively lowunit-volume market segment, making this market a lesser choice for focusing new materials development, finding a material that will survive one to ten thousand contacts with a single TIM placement is highly desirable for test throughput and cost.

|              | Table 1. Thermal/Mechanical | Cycling Test Parameters                 |                    |

|--------------|-----------------------------|-----------------------------------------|--------------------|

| Organization | Test Pressure Reported      | Test Temperature Range<br>Reported (°C) | Dwell<br>(Seconds) |

| C            | 11.7 bar (170 PSI)          | 25**/100                                | 60                 |

| Company A    | 11.7 bar (170 PSI)          | 100                                     | 60                 |

| Company B    | 6.7 bar (100 PSI)           | -                                       | 60                 |

| Company C    | -                           | 120                                     | -                  |

| Company D    | -                           | 100                                     | -                  |

| Company E    | -                           | 80                                      | 60                 |

| Communit E   | 4.1/6.7 bar (60/100 PSI)*   | 105**/125                               | -                  |

| Company F    | 6.7 bar (100 PSI)*          | 105**/125                               | -                  |

Notes: \* Pressure applied dependent upon die or package contact area. \*\* Initial value.

Development of three new materials for S/TB has therefore focused on metallic and graphitic sheet materials. Graphitic materials are difficult to adapt to sharp corners and edges of test heads and also have a potential for shedding electrically-conductive flakes and fibers. Metal TIMs also, depending on metal and alloy selected, may be relatively brittle and have potential for shredding when the test head repeatedly contacts at an angle, on a 90-degree edge or on the sharp edge of a bare die. Taken together, these requirements as outlined in *Table 1* are a significant challenge for new materials development.

#### **RELIABILITY TEST PROGRAM DEVELOPMENT**

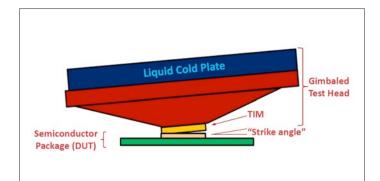

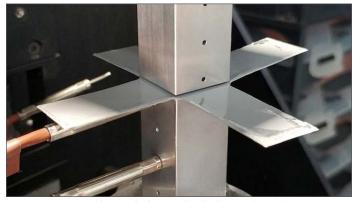

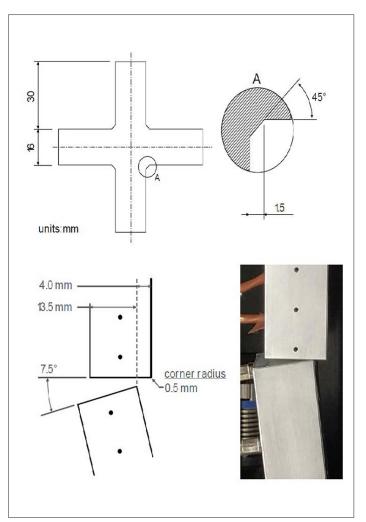

Use of a commercial TIM test stand was considered as the primary tool for a reliability test program. The ability to combine repeated, controlled cycling of a test material (for contact at a specific temperature, dwell, and release), with automated data collection per an industry-standard thermal resistance test procedure, was seen as a constructive approach, given the previously demonstrated reliability testing completed by the test stand manufacturer for other types of thermal materials. The test stand, designed and manufactured by a commercial manufacturer [1] to follow ASTM D 5470-17, incorporates servo motors with precise control of test head movement; a goniometer for planarity measurement; and internal software and motor controls. In addition, test heads are designed to be removable and in the standard system could be adapted to create a non-flat condition, with one test head capable of contacting the second at a pre-determined angle. [2, 3] This latter capability would mimic the so-called strike angle, found in high through-put semiconductor test systems where multiple types of devices (with lid; different lid sizes, different package types; bare die, and similar) flow through the test system. More complex system test heads include a gimbal, to allow the test head surface to adapt to these differences, as shown in Figure 1. [4]

Figure 1: Illustration of a semiconductor test stand gimbal-mounted test head, allowing contact of the test head with attached TIM at different orientations to different devices under test with different package configurations and contact surface dimensions. (Adapted from Sanchez, [1]).

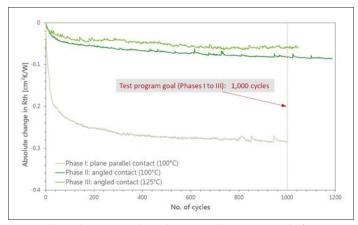

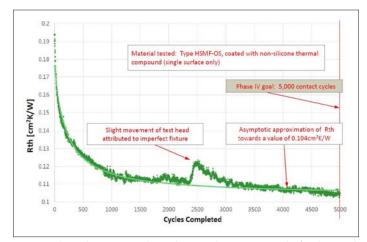

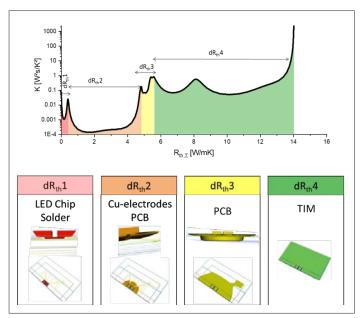

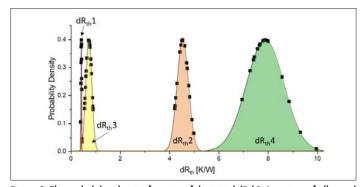

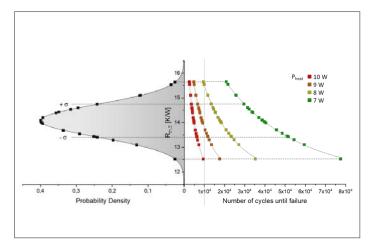

For this test program, four test phases were developed to place increasingly challenging durability requirements on each new development material; simultaneously, TIM thickness change was measured during each phase, as was thermal resistance. The four phases are summarized in *Table 2*; the first is the baseline set of data against which subsequent data sets were to be compared. Phases I and IV are similar to the conditions required for stan-

dard ASTM D 5470-17 thermal resistance testing, with parallel test heads and a uniform power and clamping force applied. [5, 6] Phases II and III address the elevated temperature and so-called "strike angle" introduced to mimic behavior in S/TB processes; the specific characteristics of these two phases were developed from the data obtained in a short industry survey of practice. Phases II and II therefore are not representative of a normal thermal resistance test per industry standard ASTM D 5470-17. (A dwell as short as sixty seconds would normally be considered to be insufficient for system stabilization and accurate data generation.) Specifications for the test heads are shown in *Table 3*.